Chińscy naukowcy zaprezentowali "Big Chip"

Naukowcy z Chińskiej Akademii Nauk uważają, że dokonali znaczącego odkrycia – układu scalonego łączącego 16 chipletów, z których każdy posiada 16 rdzeni RISC-V, połączonych ze sobą za pomocą sieci na chipie.

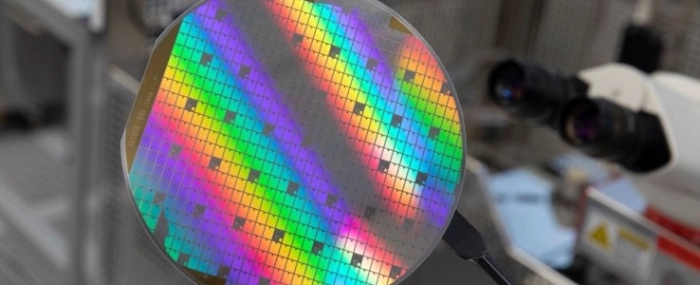

Zgodnie z wynikami badań przedstawionymi w artykule opublikowanym w czasopiśmie Fundamental Research, zespół nazwał swój projekt Big Chip i planuje skalować go do 1600 rdzeni poprzez wykorzystanie całego wafla.

Jeśli technologia się sprawdzi, jej zastosowanie może być znaczące. Każda nowa generacja chipów zwiększa gęstość tranzystorów, co utrudnia zapewnienie wymaganej wydajności. Obecnie producenci chipów szukają alternatywnych rozwiązań, aby uczynić procesory bardziej pojemnymi. Jednym z nich jest dzielenie urządzeń na chiplety i łączenie ich ze sobą, a zupełnie czymś innym jest osadzanie ich na całej płytce krzemowej. Rozważa się również połączenie obu podejść, które polega na układaniu chipów w stosy w celu zwiększenia pojemności i funkcjonalności.

Jednakże wszystkie z nich są ograniczone możliwościami sprzętu litograficznego, który jest używany do wytrawiania chipów.

Tak zwane chipy waflowe jak dotąd osiągnęła tylko jedna firma – Cerebras. Jednak wraz z tą wiadomością wydaje się, że chińscy inżynierowie zbliżają się do tego celu. W raporcie czytamy, że zbudowali oni 256-rdzeniową konstrukcję wieloprocesorową i badają sposoby przejścia na skalę waflową, wykorzystując cały wafel do zbudowania jednego dużego chipu (do 1600 rdzeni).

"Dla obecnych i przyszłych obliczeń w eksaskali przewidujemy hierarchiczną architekturę chipletów jako potężne i elastyczne rozwiązanie" – napisali naukowcy. "Hierarchiczna architektura chipletów została zaprojektowana jako wiele rdzeni i wiele chipletów z hierarchicznymi połączeniami. Wewnątrz chipletu rdzenie komunikują się za pomocą połączeń międzysystemowych o bardzo niskim opóźnieniu, podczas gdy połączenia międzyczipletowe są połączone z niskim opóźnieniem korzystnym dzięki zaawansowanej technologii pakowania, co pozwala na zminimalizowanie opóźnienia na chiplecie i uzyskanie efektu NUMA w takim systemie o wysokiej skalowalności”.