© janaka-dharmasena-dreamstime.com

Analizy |

Wielu użytkowników staje w obliczu tej kwestii w trakcie oceny czystości swoich zespołów elektronicznych. Istnieje szeroki zakres standardów, aby poradzić sobie z tą kwestią i określić metody analizy czystości powierzchni za pomocą różnych procesów. Jednak w dzisiejszych czasach prawie żaden inżynier procesu nie ma wystarczającej ilości czasu, żeby dokładnie ocenić i zrozumieć wszystkie standardy dostępne dla swoich aplikacji. Z tego powodu najważniejsze standardy oceny czystości zespołów elektronicznych zostaną przedstawione w tym artykule. Rysunek nr 1: Rozwarstwianie Lakieru.

Różne metody badań do oceny czystości zespołów elektronicznych znajdują się w normach. Jednak większość tych badań jest czasochłonna i kosztowna, dlatego artykuł dodatkowo prezentuje alternatywne sposoby, które są tańsze, a ponadto pozwalają na ich szybkie wykonanie bezpośrednio w miejscu zakończenia kontrolowanego procesu.

Gdzie wymagana jest wysoka czystość powierzchni?

W celu zapewnienia bardzo dobrej przyczepności lakieru ochronnego oraz cienkich drutów używanych procesie „wire bondingu” wymagane jest, aby powierzchnia płytki była ekstremalnie czysta. Dodatkowo w przypadku urządzeń, które będą pracowały w trudnych warunkach, częstych i gwałtownych zmianach temperatur konieczne jest usunięcie wszelkich zanieczyszczeń powstających w trakcie procesu lutowania. W przeciwnym razie zanieczyszczenia mogą powodować upływ prądu oraz elektrochemiczną migrację jonów.

Z tych powodów w artykule skoncentrowano się na następujących standardach i połączonych z nimi metodach:

- normach związanych z lakierowaniem

- normach związanych z upływem prądu

- normach związanych z procesem „bondingu”

Wykaz norm oceny

Wszystkie standardy dotyczące kwalifikacji czystości zespołów są wymienione poniżej:

Rysunek nr 1: Rozwarstwianie Lakieru.

Różne metody badań do oceny czystości zespołów elektronicznych znajdują się w normach. Jednak większość tych badań jest czasochłonna i kosztowna, dlatego artykuł dodatkowo prezentuje alternatywne sposoby, które są tańsze, a ponadto pozwalają na ich szybkie wykonanie bezpośrednio w miejscu zakończenia kontrolowanego procesu.

Gdzie wymagana jest wysoka czystość powierzchni?

W celu zapewnienia bardzo dobrej przyczepności lakieru ochronnego oraz cienkich drutów używanych procesie „wire bondingu” wymagane jest, aby powierzchnia płytki była ekstremalnie czysta. Dodatkowo w przypadku urządzeń, które będą pracowały w trudnych warunkach, częstych i gwałtownych zmianach temperatur konieczne jest usunięcie wszelkich zanieczyszczeń powstających w trakcie procesu lutowania. W przeciwnym razie zanieczyszczenia mogą powodować upływ prądu oraz elektrochemiczną migrację jonów.

Z tych powodów w artykule skoncentrowano się na następujących standardach i połączonych z nimi metodach:

- normach związanych z lakierowaniem

- normach związanych z upływem prądu

- normach związanych z procesem „bondingu”

Wykaz norm oceny

Wszystkie standardy dotyczące kwalifikacji czystości zespołów są wymienione poniżej: Ponadto w wyniku występowanie aktywatorów może pojawić się elektrolit, który sprzyja elektromigracji. Wstępna

Ponadto w wyniku występowanie aktywatorów może pojawić się elektrolit, który sprzyja elektromigracji. Wstępna  ocena powinna rozpocząć się od wizualnej inspekcji pod mikroskopem przy powiększeniu 10 do 40 razy. Przykłady jak powinien wyglądać element można odnaleźć w normie IPC-A-610 w sekcji 10.4.

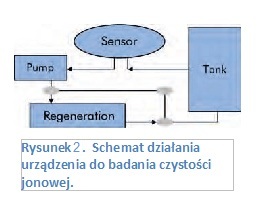

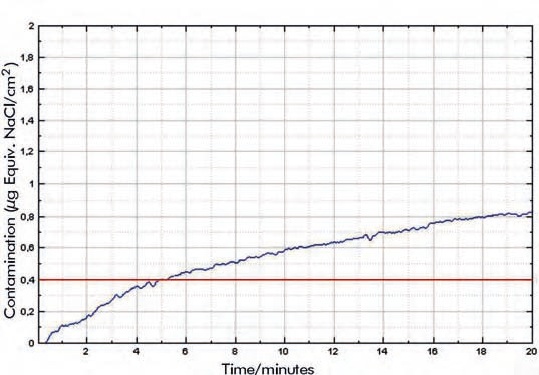

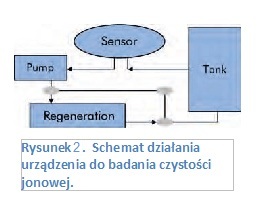

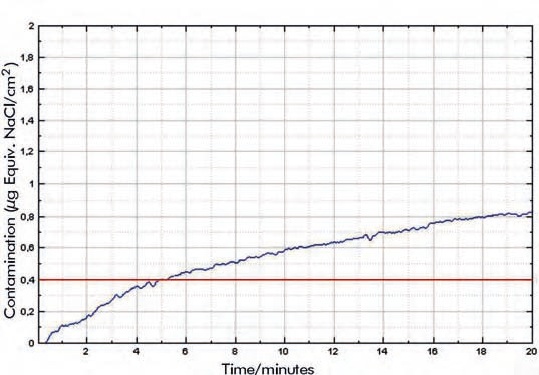

Sprawdzenie występowania higroskopijnych pozostałości aktywatorów jest wykonywane poprzez pomiar czystości jonowej znany jako ekwiwalent soli (rysunek 2). Ten ekwiwalent jest na ogół określany wg sposobu , który jest opisany normie IPC-TM-650 „Ręczne metody testowania” rozdział 2.3.25 przy użyciu roztworu wody i 2-propanolu o stężeniu 75% lub 50%.

Sposób oceny opiera się na normie IPC J-STD-001D. Należy zauważyć, że określony próg 1,56 µg NaCl na cm2 dotyczy topników o klasyfikacji ROL0 i ROL1. Nowoczesne topniki powodują jednak mniej zanieczyszczeń. Na przykład umyte zespoły elektroniczne wykazują czystość jonową na poziomie 0,1 – 0,4 µg/cm2 oraz 0,4 – 0,7 µg/cm2 dla systemów topnikowych No-Clean, z powodu hermetyzacji higroskopijnych aktywatorów. Dlatego w celu zapewnienia niezawodnej powłoki konieczne jest zapewnienie czystości jonowej poniżej 0,4 µg/cm2 (rysunek 3).

ocena powinna rozpocząć się od wizualnej inspekcji pod mikroskopem przy powiększeniu 10 do 40 razy. Przykłady jak powinien wyglądać element można odnaleźć w normie IPC-A-610 w sekcji 10.4.

Sprawdzenie występowania higroskopijnych pozostałości aktywatorów jest wykonywane poprzez pomiar czystości jonowej znany jako ekwiwalent soli (rysunek 2). Ten ekwiwalent jest na ogół określany wg sposobu , który jest opisany normie IPC-TM-650 „Ręczne metody testowania” rozdział 2.3.25 przy użyciu roztworu wody i 2-propanolu o stężeniu 75% lub 50%.

Sposób oceny opiera się na normie IPC J-STD-001D. Należy zauważyć, że określony próg 1,56 µg NaCl na cm2 dotyczy topników o klasyfikacji ROL0 i ROL1. Nowoczesne topniki powodują jednak mniej zanieczyszczeń. Na przykład umyte zespoły elektroniczne wykazują czystość jonową na poziomie 0,1 – 0,4 µg/cm2 oraz 0,4 – 0,7 µg/cm2 dla systemów topnikowych No-Clean, z powodu hermetyzacji higroskopijnych aktywatorów. Dlatego w celu zapewnienia niezawodnej powłoki konieczne jest zapewnienie czystości jonowej poniżej 0,4 µg/cm2 (rysunek 3).

Pomiary czystości mają pewne ograniczenie ponieważ mówią jedynie o poziomie zanieczyszczeń całej płytki i nie pozawalają na określenie ich lokalizacji na płytce. Znajomość lokalizacji tych zanieczyszczeń jest niezwykle ważna do oceny ich wpływu na niezawodność elementu.

Pomiary czystości mają pewne ograniczenie ponieważ mówią jedynie o poziomie zanieczyszczeń całej płytki i nie pozawalają na określenie ich lokalizacji na płytce. Znajomość lokalizacji tych zanieczyszczeń jest niezwykle ważna do oceny ich wpływu na niezawodność elementu.

zanieczyszczenia, które w połączeniu z wilgocią mogą sprzyjać powstawaniu elektrolitów. Z tego powodu zespół musi być wizualnie sprawdzony oraz nie może zawierać higroskopijnych pozostałości aktywatorów. Metoda oceny czystości powinna zostać przeprowadzona dokładnie w taki sam sposób jak w części tego artykułu pt. „Czystość topników/pozostałości aktywatorów” przy wykorzystaniu mikroskopu o powiększeniu 10-40 x oraz jednej z metod diagnozowania pozostałości aktywator np. Zestron Flux Test.

Istotnym czynnikiem związanym z upływem prądu jest rezystancja powierzchniowa (SIR). Im wyższa rezystancja powierzchniowa tym ryzyko powstania zjawiska upływu prądu mniejsze. Sposób określania rezystancji powierzchniowej jest opisany w normie IPC-TM-650, do tego celu wykorzystywane są specjalne płyty grzebieniowe. Określony w tej normie próg wynosi 108 ohma.

Maksymalna czystość mysi być także zachowana w przypadku stosowania procesu wire bondingu. Z tego powodu właściwe dla tego procesu parametry czystości są opisane poniżej.

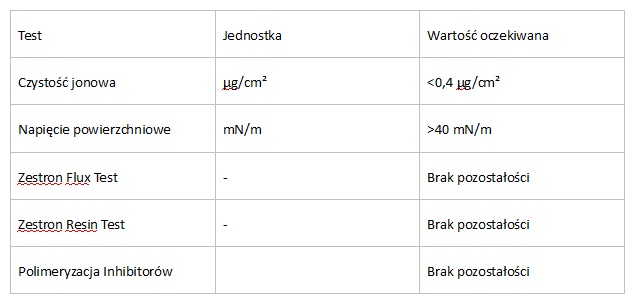

Parametry dla osiągnięcia niezawodnych powłok ochronnych i stabilnych połączeń

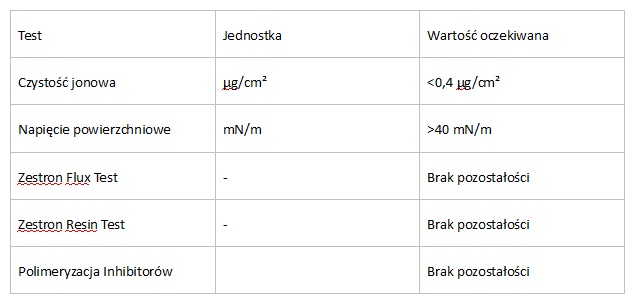

Grupa robocza GfKOOR na podstawie własnych testów oraz współpracy z różnymi firmami przedstawiała w opracowaniu „Ochrona przed korozją zespołów elektronicznych” wykaz parametrów, które gwarantują niezawodną powłokę ochronną. Wspólnie z F&K Delvotec, Zestron wykonał podobne badania, wykaz tych wartości znajduje się w Tabeli 1. Dzięki tym paramentom, w łatwy i szybki sposób można ocenić przygotowanie powierzchni do wykonania niezawodnej powłoki ochronnej.

Podsumowanie

Zapewnienie wymienionych w tym artykule parametrów gwarantuje brak problemów związanych z upływem prądu oraz jakością powłoki ochronnej związanych z czystością powierzchni. Nie zawsze do oceny czystości zespołów elektronicznych konieczne jest wykorzystanie kosztownych i czasochłonnych metod. Zaprezentowane alternatywne metody badań, które mogą być wykorzystywane na produkcji bezpośrednio po zakończeniu procesu pozwalają na wyciągnięcie wiarygodnych wniosków dotyczących czystości powierzchni.

Jakub Opałka

© PB Technik

zanieczyszczenia, które w połączeniu z wilgocią mogą sprzyjać powstawaniu elektrolitów. Z tego powodu zespół musi być wizualnie sprawdzony oraz nie może zawierać higroskopijnych pozostałości aktywatorów. Metoda oceny czystości powinna zostać przeprowadzona dokładnie w taki sam sposób jak w części tego artykułu pt. „Czystość topników/pozostałości aktywatorów” przy wykorzystaniu mikroskopu o powiększeniu 10-40 x oraz jednej z metod diagnozowania pozostałości aktywator np. Zestron Flux Test.

Istotnym czynnikiem związanym z upływem prądu jest rezystancja powierzchniowa (SIR). Im wyższa rezystancja powierzchniowa tym ryzyko powstania zjawiska upływu prądu mniejsze. Sposób określania rezystancji powierzchniowej jest opisany w normie IPC-TM-650, do tego celu wykorzystywane są specjalne płyty grzebieniowe. Określony w tej normie próg wynosi 108 ohma.

Maksymalna czystość mysi być także zachowana w przypadku stosowania procesu wire bondingu. Z tego powodu właściwe dla tego procesu parametry czystości są opisane poniżej.

Parametry dla osiągnięcia niezawodnych powłok ochronnych i stabilnych połączeń

Grupa robocza GfKOOR na podstawie własnych testów oraz współpracy z różnymi firmami przedstawiała w opracowaniu „Ochrona przed korozją zespołów elektronicznych” wykaz parametrów, które gwarantują niezawodną powłokę ochronną. Wspólnie z F&K Delvotec, Zestron wykonał podobne badania, wykaz tych wartości znajduje się w Tabeli 1. Dzięki tym paramentom, w łatwy i szybki sposób można ocenić przygotowanie powierzchni do wykonania niezawodnej powłoki ochronnej.

Podsumowanie

Zapewnienie wymienionych w tym artykule parametrów gwarantuje brak problemów związanych z upływem prądu oraz jakością powłoki ochronnej związanych z czystością powierzchni. Nie zawsze do oceny czystości zespołów elektronicznych konieczne jest wykorzystanie kosztownych i czasochłonnych metod. Zaprezentowane alternatywne metody badań, które mogą być wykorzystywane na produkcji bezpośrednio po zakończeniu procesu pozwalają na wyciągnięcie wiarygodnych wniosków dotyczących czystości powierzchni.

Jakub Opałka

© PB Technik

Jak czyste muszą być moduły elektroniczne?

Zapraszamy do artykułu technicznego o najważniejszych standardach oceny czystości podzespołów elektronicznych.

Wielu użytkowników staje w obliczu tej kwestii w trakcie oceny czystości swoich zespołów elektronicznych. Istnieje szeroki zakres standardów, aby poradzić sobie z tą kwestią i określić metody analizy czystości powierzchni za pomocą różnych procesów. Jednak w dzisiejszych czasach prawie żaden inżynier procesu nie ma wystarczającej ilości czasu, żeby dokładnie ocenić i zrozumieć wszystkie standardy dostępne dla swoich aplikacji. Z tego powodu najważniejsze standardy oceny czystości zespołów elektronicznych zostaną przedstawione w tym artykule.

Rysunek nr 1: Rozwarstwianie Lakieru.

Różne metody badań do oceny czystości zespołów elektronicznych znajdują się w normach. Jednak większość tych badań jest czasochłonna i kosztowna, dlatego artykuł dodatkowo prezentuje alternatywne sposoby, które są tańsze, a ponadto pozwalają na ich szybkie wykonanie bezpośrednio w miejscu zakończenia kontrolowanego procesu.

Gdzie wymagana jest wysoka czystość powierzchni?

W celu zapewnienia bardzo dobrej przyczepności lakieru ochronnego oraz cienkich drutów używanych procesie „wire bondingu” wymagane jest, aby powierzchnia płytki była ekstremalnie czysta. Dodatkowo w przypadku urządzeń, które będą pracowały w trudnych warunkach, częstych i gwałtownych zmianach temperatur konieczne jest usunięcie wszelkich zanieczyszczeń powstających w trakcie procesu lutowania. W przeciwnym razie zanieczyszczenia mogą powodować upływ prądu oraz elektrochemiczną migrację jonów.

Z tych powodów w artykule skoncentrowano się na następujących standardach i połączonych z nimi metodach:

- normach związanych z lakierowaniem

- normach związanych z upływem prądu

- normach związanych z procesem „bondingu”

Wykaz norm oceny

Wszystkie standardy dotyczące kwalifikacji czystości zespołów są wymienione poniżej:

Rysunek nr 1: Rozwarstwianie Lakieru.

Różne metody badań do oceny czystości zespołów elektronicznych znajdują się w normach. Jednak większość tych badań jest czasochłonna i kosztowna, dlatego artykuł dodatkowo prezentuje alternatywne sposoby, które są tańsze, a ponadto pozwalają na ich szybkie wykonanie bezpośrednio w miejscu zakończenia kontrolowanego procesu.

Gdzie wymagana jest wysoka czystość powierzchni?

W celu zapewnienia bardzo dobrej przyczepności lakieru ochronnego oraz cienkich drutów używanych procesie „wire bondingu” wymagane jest, aby powierzchnia płytki była ekstremalnie czysta. Dodatkowo w przypadku urządzeń, które będą pracowały w trudnych warunkach, częstych i gwałtownych zmianach temperatur konieczne jest usunięcie wszelkich zanieczyszczeń powstających w trakcie procesu lutowania. W przeciwnym razie zanieczyszczenia mogą powodować upływ prądu oraz elektrochemiczną migrację jonów.

Z tych powodów w artykule skoncentrowano się na następujących standardach i połączonych z nimi metodach:

- normach związanych z lakierowaniem

- normach związanych z upływem prądu

- normach związanych z procesem „bondingu”

Wykaz norm oceny

Wszystkie standardy dotyczące kwalifikacji czystości zespołów są wymienione poniżej:- IPC JST-001 (rozdział 8) „Wymagania dotyczące lutowanych zespołów elektrycznych i elektronicznych” opisuje metody i wymagania dotyczące produkcji elektronicznej

- IPC-A-610 (sekcja 10.4) „Dopuszczalność zespołów elektronicznych” Wizualna dokumentacja precyzująca jakościowe wymagania zespołów elektronicznych prezentująca najlepsze i najgorsze przypadki

- IPC TM 650 „Przewodnik po metodach testowania” Zbiór różnych metod testowania urządzeń elektronicznych

- IPC TP 1113 (Dokumentacja Techniczna) „Pomiar czystości jonowej obwodów drukowanych. Co właściwie nam mówi?” Opisuje metody i ograniczenia pomiaru czystości jonowej i wpływ różnych rodzajów topników na jego wynik

- IEC-68-2 jest znormalizowaną metodą wykonywania testów klimatycznych zespołów elektronicznych

- The GfKORR Guidelines „Przewodnik po procesie lakierowania ochronnego” Jest uzupełnieniem przewodnika IPC- HDBK-830, który dotyczy niezawodności powłok ochronnych.

- Czystość jonowa/pozostałości aktywatorów

- Pozostałości żywic i zwilżalność powierzchni

- Utwardzanie lakieru i niezawodność

Ponadto w wyniku występowanie aktywatorów może pojawić się elektrolit, który sprzyja elektromigracji. Wstępna

Ponadto w wyniku występowanie aktywatorów może pojawić się elektrolit, który sprzyja elektromigracji. Wstępna  ocena powinna rozpocząć się od wizualnej inspekcji pod mikroskopem przy powiększeniu 10 do 40 razy. Przykłady jak powinien wyglądać element można odnaleźć w normie IPC-A-610 w sekcji 10.4.

Sprawdzenie występowania higroskopijnych pozostałości aktywatorów jest wykonywane poprzez pomiar czystości jonowej znany jako ekwiwalent soli (rysunek 2). Ten ekwiwalent jest na ogół określany wg sposobu , który jest opisany normie IPC-TM-650 „Ręczne metody testowania” rozdział 2.3.25 przy użyciu roztworu wody i 2-propanolu o stężeniu 75% lub 50%.

Sposób oceny opiera się na normie IPC J-STD-001D. Należy zauważyć, że określony próg 1,56 µg NaCl na cm2 dotyczy topników o klasyfikacji ROL0 i ROL1. Nowoczesne topniki powodują jednak mniej zanieczyszczeń. Na przykład umyte zespoły elektroniczne wykazują czystość jonową na poziomie 0,1 – 0,4 µg/cm2 oraz 0,4 – 0,7 µg/cm2 dla systemów topnikowych No-Clean, z powodu hermetyzacji higroskopijnych aktywatorów. Dlatego w celu zapewnienia niezawodnej powłoki konieczne jest zapewnienie czystości jonowej poniżej 0,4 µg/cm2 (rysunek 3).

ocena powinna rozpocząć się od wizualnej inspekcji pod mikroskopem przy powiększeniu 10 do 40 razy. Przykłady jak powinien wyglądać element można odnaleźć w normie IPC-A-610 w sekcji 10.4.

Sprawdzenie występowania higroskopijnych pozostałości aktywatorów jest wykonywane poprzez pomiar czystości jonowej znany jako ekwiwalent soli (rysunek 2). Ten ekwiwalent jest na ogół określany wg sposobu , który jest opisany normie IPC-TM-650 „Ręczne metody testowania” rozdział 2.3.25 przy użyciu roztworu wody i 2-propanolu o stężeniu 75% lub 50%.

Sposób oceny opiera się na normie IPC J-STD-001D. Należy zauważyć, że określony próg 1,56 µg NaCl na cm2 dotyczy topników o klasyfikacji ROL0 i ROL1. Nowoczesne topniki powodują jednak mniej zanieczyszczeń. Na przykład umyte zespoły elektroniczne wykazują czystość jonową na poziomie 0,1 – 0,4 µg/cm2 oraz 0,4 – 0,7 µg/cm2 dla systemów topnikowych No-Clean, z powodu hermetyzacji higroskopijnych aktywatorów. Dlatego w celu zapewnienia niezawodnej powłoki konieczne jest zapewnienie czystości jonowej poniżej 0,4 µg/cm2 (rysunek 3).

Pomiary czystości mają pewne ograniczenie ponieważ mówią jedynie o poziomie zanieczyszczeń całej płytki i nie pozawalają na określenie ich lokalizacji na płytce. Znajomość lokalizacji tych zanieczyszczeń jest niezwykle ważna do oceny ich wpływu na niezawodność elementu.

Pomiary czystości mają pewne ograniczenie ponieważ mówią jedynie o poziomie zanieczyszczeń całej płytki i nie pozawalają na określenie ich lokalizacji na płytce. Znajomość lokalizacji tych zanieczyszczeń jest niezwykle ważna do oceny ich wpływu na niezawodność elementu.

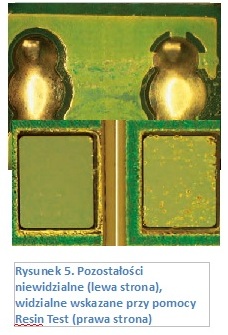

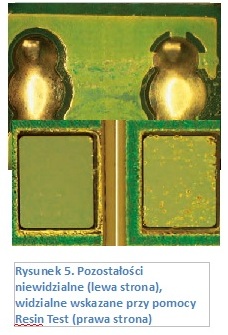

Przez lata jedyną możliwością do znalezienia dokładnej miejsca zanieczyszczeń było wykonanie zdjęcia przy użyciu mikroskopu elektronowego. Niestety ta metoda pochłania bardzo dużo czasu i nie nadaje się do wykonywania w warunkach produkcyjnych. W między czasie zostały zaprezentowane nowe metody (takie jak Zestron FLux Test) które selektywnie demonstrują obecność aktywatorów poprzez reakcję chemiczną zmieniając kolor w miejscu występowania aktywatorów (rysunek 4). W ten sposób Zestron Flux Test umożliwia szybką lokalizację aktywatorów w warunkach produkcyjnych. Pozostałości żywic Dodatkową przeszkodą w zapewnieniu niezawodnej powłoki ochronnej na zespole elektronicznym jest obecność żywic. Jeżeli powłoka ochronna będzie nakładana na żywice w tym miejscu zwilżalność i przyczepność będzie niewystarczająca. Ponadto z uwagi na różne współczynniki rozszerzalności cieplnej w trakcie pracy urządzenia na powłoce ochronnej mogą pojawić się pęknięcia. Ilość pozostałości żywic jest określona w normie IPC J-STD-001D w sekcji 8.3.6.1.. Dla urządzeń klasy 3 wymagany jest poziom < 40 µg/cm², co w przybliżeniu oznacza obecność żywicy na jednym pojedynczym lucie. W normie IPC-TM-650 w sekcji 2.3.27.1 zaprezentowana jest metoda pomiaru obecności żywic - HPLC (high performance liquid chromatography). Metoda ta jest także bardzo czasochłonna i droga co jednocześnie uniemożliwia jest stosowanie w normalnych warunkach produkcyjnych. Prostszym i tańszym rozwiązaniem jest wykonanie testu przy pomocy Zestron Resin Test. Ten szybki test selektywnie prezentuje obecność żywic podobnie jak w przypadku Flux Test, prezentuje obecność żywic poprzez zmianę koloru w miejscu ich występowania. Analiza powierzchni żywic oraz ilości pozostałości aktywatorów, jak również określenie czystości jonowej zespołu są zatem najważniejszym metodami do oceny przygotowania naszej powierzchni przed położeniem powłoki ochronnej. Istotną częścią wpływającą na jakość powłoki ochronnej jest proces utwardzania. Różne czynniki mogą go hamować. Znane są różne metody do sprawdzania poprawności utwardzania. Utwardzanie powłoki ochronnej i jej niezawodność W zależności od typu powłoki ochronnej, organiczne pozostałości po procesie lutowania mogą działać jak czynniki hamujące polimeryzację. Ponadto związki siarki oraz amoniak, które czasem są zawarte w topnikach mogą także działać w podobny sposób. Zanieczyszczenia te są zwykle identyfikowane przy pomocy skaningowego mikroskopu elektronowego. Także i w tym wypadku istnieją tańsze i szybsze metody bardziej nadające się dla warunków produkcyjnych. Jednym z nich jest pełny test żywotności powłoki opisany w normie IEC 68-2. Jednakże prezentowany test musi być wykonany na finalnym produkcie, a ponadto wciąż jest długotrwały i może trwać nawet do 6 miesięcy. Szybsza i tańsza metoda, która może być zastosowana na każdym etapie produkcji znana jest jako CoRe (Coating Relibility). Metoda ta bardziej dokładnie opisana jest w przewodniku organizacji GfKORR pt „Przewodnik po używaniu i nakładaniu powłok ochronnych” Poprzez całkowite zanurzenie pokrytego powłoką ochronną zespołu elektronicznego w dejonizowanej wodzie mechanizm elektromigracji jonów jest znacząco przyśpieszony. Dlatego wnioski dotyczące niezawodności powłoki mogą być sporządzone w ciągu kilku godzin, a nie miesięcy. Niezawodnej pracy oczekujemy także od urządzeń, które nie będą pokrywane żadną powłoką ochronną. Dla tych urządzeń głównie brane są pod uwagę zagadnienia zwane ogólnie pod hasłem upływ prądu. Dlatego zagadnienie także istnieją odpowiednie normy i metody testów. Wymagania dotyczące ochrony przed upływem prądu Aby zapobiegać upływowi prądu na płytce (rysunek 5) na naszym zespole nie mogą występować żadneRysunek 4.

zanieczyszczenia, które w połączeniu z wilgocią mogą sprzyjać powstawaniu elektrolitów. Z tego powodu zespół musi być wizualnie sprawdzony oraz nie może zawierać higroskopijnych pozostałości aktywatorów. Metoda oceny czystości powinna zostać przeprowadzona dokładnie w taki sam sposób jak w części tego artykułu pt. „Czystość topników/pozostałości aktywatorów” przy wykorzystaniu mikroskopu o powiększeniu 10-40 x oraz jednej z metod diagnozowania pozostałości aktywator np. Zestron Flux Test.

Istotnym czynnikiem związanym z upływem prądu jest rezystancja powierzchniowa (SIR). Im wyższa rezystancja powierzchniowa tym ryzyko powstania zjawiska upływu prądu mniejsze. Sposób określania rezystancji powierzchniowej jest opisany w normie IPC-TM-650, do tego celu wykorzystywane są specjalne płyty grzebieniowe. Określony w tej normie próg wynosi 108 ohma.

Maksymalna czystość mysi być także zachowana w przypadku stosowania procesu wire bondingu. Z tego powodu właściwe dla tego procesu parametry czystości są opisane poniżej.

Parametry dla osiągnięcia niezawodnych powłok ochronnych i stabilnych połączeń

Grupa robocza GfKOOR na podstawie własnych testów oraz współpracy z różnymi firmami przedstawiała w opracowaniu „Ochrona przed korozją zespołów elektronicznych” wykaz parametrów, które gwarantują niezawodną powłokę ochronną. Wspólnie z F&K Delvotec, Zestron wykonał podobne badania, wykaz tych wartości znajduje się w Tabeli 1. Dzięki tym paramentom, w łatwy i szybki sposób można ocenić przygotowanie powierzchni do wykonania niezawodnej powłoki ochronnej.

Podsumowanie

Zapewnienie wymienionych w tym artykule parametrów gwarantuje brak problemów związanych z upływem prądu oraz jakością powłoki ochronnej związanych z czystością powierzchni. Nie zawsze do oceny czystości zespołów elektronicznych konieczne jest wykorzystanie kosztownych i czasochłonnych metod. Zaprezentowane alternatywne metody badań, które mogą być wykorzystywane na produkcji bezpośrednio po zakończeniu procesu pozwalają na wyciągnięcie wiarygodnych wniosków dotyczących czystości powierzchni.

Jakub Opałka

© PB Technik

zanieczyszczenia, które w połączeniu z wilgocią mogą sprzyjać powstawaniu elektrolitów. Z tego powodu zespół musi być wizualnie sprawdzony oraz nie może zawierać higroskopijnych pozostałości aktywatorów. Metoda oceny czystości powinna zostać przeprowadzona dokładnie w taki sam sposób jak w części tego artykułu pt. „Czystość topników/pozostałości aktywatorów” przy wykorzystaniu mikroskopu o powiększeniu 10-40 x oraz jednej z metod diagnozowania pozostałości aktywator np. Zestron Flux Test.

Istotnym czynnikiem związanym z upływem prądu jest rezystancja powierzchniowa (SIR). Im wyższa rezystancja powierzchniowa tym ryzyko powstania zjawiska upływu prądu mniejsze. Sposób określania rezystancji powierzchniowej jest opisany w normie IPC-TM-650, do tego celu wykorzystywane są specjalne płyty grzebieniowe. Określony w tej normie próg wynosi 108 ohma.

Maksymalna czystość mysi być także zachowana w przypadku stosowania procesu wire bondingu. Z tego powodu właściwe dla tego procesu parametry czystości są opisane poniżej.

Parametry dla osiągnięcia niezawodnych powłok ochronnych i stabilnych połączeń

Grupa robocza GfKOOR na podstawie własnych testów oraz współpracy z różnymi firmami przedstawiała w opracowaniu „Ochrona przed korozją zespołów elektronicznych” wykaz parametrów, które gwarantują niezawodną powłokę ochronną. Wspólnie z F&K Delvotec, Zestron wykonał podobne badania, wykaz tych wartości znajduje się w Tabeli 1. Dzięki tym paramentom, w łatwy i szybki sposób można ocenić przygotowanie powierzchni do wykonania niezawodnej powłoki ochronnej.

Podsumowanie

Zapewnienie wymienionych w tym artykule parametrów gwarantuje brak problemów związanych z upływem prądu oraz jakością powłoki ochronnej związanych z czystością powierzchni. Nie zawsze do oceny czystości zespołów elektronicznych konieczne jest wykorzystanie kosztownych i czasochłonnych metod. Zaprezentowane alternatywne metody badań, które mogą być wykorzystywane na produkcji bezpośrednio po zakończeniu procesu pozwalają na wyciągnięcie wiarygodnych wniosków dotyczących czystości powierzchni.

Jakub Opałka

© PB Technik