© Evertiq

Komponenty |

Rewolucja w FPGA dla AI i ML – przełomowa przepustowość i wydajność obliczeniowa

Achronix opracowało przełomowe układy FPGA, oparte na innowacyjnej architekturze, której sercem są niezwykłe 2D NoC. To dzięki nim nie ma wąskich gardeł w wewnętrznej komunikacji, a wszystko dzieje się super-szybko, wydajnie i bardzo niezawodnie.

Firma Achronix Semiconductor to lider w sferze układów będących dedykowanymi akceleratorami sprzętowymi i wysoce wydajnych układów eFPGA. Zaprezentowali oni nową, innowacyjną rodzinę układów FPGA, która ma sprostać rosnącym wymaganiom sztucznej inteligencji (AI) i uczenia maszynowego (ML), a także aplikacjom wymagającym bardzo wysokiej przepustowości i mocy obliczeniowej.

Mowa tu o rodzinie Achronix Speedster 7t, którą oparto na nowej, wysoce zoptymalizowanej architekturze, która pozwala wyjść poza tradycyjne rozwiązania FPGA, oferując świetną wydajność ASIC, zdolności adaptacyjne FPGA oraz dodatkowe funkcje usprawniające aplikacje i same procesy projektowania.

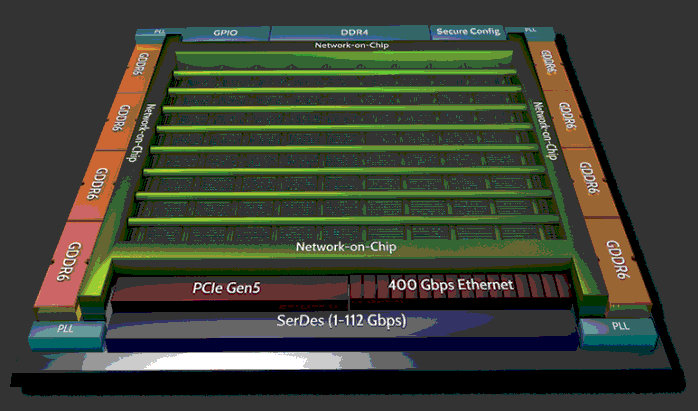

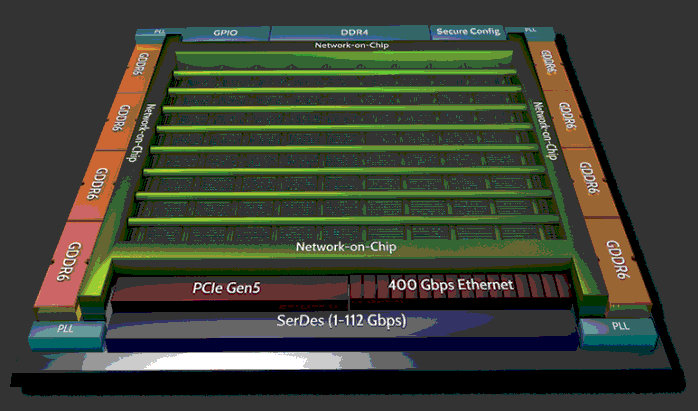

Nowa rodzina Speedster 7t wykorzystuje rewolucyjne układy 2D Network-on-Chip (NoC), a także gęstą sieć nowych procesorów uczenia maszynowego (MLP). Łącząc programowalność FPGA ze strukturami routingu ASIC oraz mocnymi silnikami obliczeniowymi, rodzina Speedster7t tworzyć ma nową klasę technologii „FPGA”.

Aplikacje AI i ML obecnie bardzo szybko się zmieniają. Speedster 7t ma wspomagać te procesy, łącząc wymagania dotyczące wysokiej wydajności, elastyczności, a także przyśpieszania wprowadzania nowych rozwiązań na rynek.

Firma Semico Research Corp. przewiduje, że wielkość rynku FPGA w aplikacjach AI wzrośnie o 3-krotnie, w ciągu najbliższych czterech lat, osiągając wartość do 5,2 mld USD.

Opracowując rodzinę układów FPGA Speedster7t, zespół inżynierów Achronix przeprojektował całą architekturę FPGA, aby zrównoważyć efektywność przetwarzania w układzie, elementy strukturalnej łączności wewnętrznej i zewnętrznych portów I/O, aby zmaksymalizować przepustowość obciążeń wymagających dużej ilości danych. Przykładem takich aplikacji mogą być te występujące w systemach „edge”, serwerach AI / ML, aplikacjach sieciowych i pamięci masowych.

Układy stworzone zostały z wykorzystaniem procesów i technologii FinFET TSMC 7 nm. Oprócz wbudowanych wysoce wydajnych układów przetwarzających, Speedster 7t posiadać mają wsparcie interfejsów GDDR6, Ethernet 400G oraz PCI Express generacji 5. Całość spleciono tak, by osiągnąć najwyższą przepustowość klasy ASIC, zachowując przy tym pełną programowalność układów FPGA.

© Achronix

Optymalizacja pod wydajność obliczeniową

Sercem Speedster 7t ma być masowa sieć równolegle połączonych ze sobą programowalnych elementów obliczeniowych MLP, zapewniającymi najwyższą w tej branży gęstość obliczeniową. MLP to wysoce konfigurowalne bloki obliczeniowe (przetwarzania intensywnego), obsługujące formaty od 4 do 24 bitów, wspierane przez wydajne tryby zmiennoprzecinkowe. Znajdziemy tu też bezpośrednie wsparcie dla 16-bitowego formatu TensorFlow, a także format zmiennoprzecinkowy bloku doładowanego, który podwaja liczbę silników obliczeniowych MLP.

MLP są ściśle sprzężone z wbudowanymi blokami pamięci, eliminując tradycyjne opóźnienia związane z routingiem FPGA. Zapewnia to dostarczanie danych do MLP z maksymalną wydajnością przy 750 MHz. To połączenie wysokiej gęstości obliczeniowej i wysokiej przepustowości zapewnia najwyższą użyteczność operacji na sekundę (Tops), spośród zbliżonych układów tego typu.

Światowa przepustowość

Krytyczne dla uczenia się maszynowego i wysoce wydajnych systemów obliczeniowych, jest osiąganie dużej przepustowości do pamięci poza układem, w celu budowania źródeł danych i buforów. Speedster 7t są pierwszymi i jedynymi układami na rynku, wspierającymi interfejs GDDR6, oferując najwyższą na rynku przepustowość do pamięci zewnętrznych.

Każdy z wbudowanych kontrolerów GDDR6 umożliwia transfer na poziomie 512 Gbps, a w układzie Speedster mamy ich osiem. Pozwala to na osiąganie łącznej przepustowości na poziomie 4 Tbps. Jest to równoważność przepustowości systemów HBM, lecz dużo niższym kosztem.

Wsparcie GDDR6 to nie jedyna przewaga tych układów w sferze przepustowości. W strukturze Speedster 7t zawarto 72 najwyższej klasy SerDes, które obsługiwać mają prędkości od 1 do 122 Gbps. Są tu też wspomniane układy MAC Ethernet 400G z korekcją błędów FEC (wspierające konfiguracje 4x 100G lub 8x 50 G), a także kontrolery PCI Express Gen5 (8- i 16-liniowe).

Wydajność transferowa

Wspomniane elementy i parametry przytłoczyłyby klasyczne routingi FPGA. Z tego też względu Speedster 7t zawiera nowoczesny, innowacyjny, szerokopasmowy i dwukierunkowy NoC 2D, rozciągający się w dwóch płaszczyznach na strukturze FPGA, łącząc się ze wszystkimi jego elementami, interfejsami, itp. Działa niczym sieć autostrad nad miejskim systemem szybkich połączeń.

Każdy wiersz i kolumna NoC zaimplementowana jest jako podwójne jednokierunkowe, 256-bitowe kanały AXI, działające na paśmie 2 GHz, dostarczając przepustowość na poziomie 512 Gbps w każdym kierunku, równocześnie. Uproszcza to tym samym superszybkie przesyłanie danych wewnątrz układu, zapewniając łatwe kierowanie strumieni danych do dowolnych, nawet niestandardowych silników przetwarzających. NoC ponadto ma za zadanie wyeliminować jakiekolwiek wąskie gardła w systemie łączeniowym, występujące w klasycznych konstrukcjach FPGA (korzystające z programowalnego routingi i tablic LUT). Rozwiązanie to też znacząco wpływa na redukcję zużycia energii.

A bezpieczeństwo?

Speedster 7t wspierać ma najnowocześniejsze funkcje zabezpieczające bitstream z wieloma warstwami obronnymi, zapewniając wysoki stopień ochrony poufnych danych oraz chroniąc integralność strumienia bitów. Jak podają twórcy, układom tym nie straszne jakiekolwiek ataki.

Klucze są szyfrowane w oparciu o funkcje PUF odporne na manipulacje fizyczne. Strumienie bitów są szyfrowane i uwierzytelniane za pomocą 256-bitowego AES-GCM. Strumienie bitów są dodatkowo dzielone na specjalne segmenty, by uchronić się przed atakami boczno-kanałowymi. Każdy segment prowadzony jest osobnymi kluczami. System deszyfrowania z kolei wykorzystuje różnicową analizę mocy (DPA). Klucz publiczny RSA jest uwierzytelniany za pomocą dedykowanego protokołu 2048-bitowego.

Wszechstronność i wygoda

Firma Achronix oferuje zarówno samodzielne układy FPGA, jak również systemy IP FPGA Speedcore, a które oparte są na tych samych technologiach. Pozwala to na płynną konwersję z Speedster 7t FPGA na ASIC.

Aplikacje FPGA zazwyczaj mają funkcje, które muszą pozostać programowalne, podczas gdy inne pozostać mogą stałymi funkcjami dedykowanymi konkretnej aplikacji systemowej. W przypadku konwersji ASIC stałe funkcje mogą zostać przeniesione w formę sprzętowej struktury ASIC, co zmniejsza rozmiar matrycy, koszt i moc. Klienci mogą spodziewać się redukcji mocy nawet o 50 procent i obniżenia kosztów o 90 procent, gdy wykorzystają Speedcore eFPGA IP do konwersji FPGA Speedster7t na dedykowane układy ASIC, pod konkretne, ostateczne projekty aplikacji.

Dostępność

Układy FPGA Speedster 7t mają być oferowane w wariantach od 363 k do 2.6 M jednostek obliczeniowych, 6-wejściowych LUT. Narzędzia wspomagające projektowanie (ACE), zawierające wsparcie dla Speedster FPGA i Speedcore eFPGA, są już dostępne.

Na pierwsze układy z nowej rodziny przyjdzie nam poczekać do czwartego kwartału 2019. Podobnie rzecz się ma z płytkami deweloperskimi.

© Achronix

Optymalizacja pod wydajność obliczeniową

Sercem Speedster 7t ma być masowa sieć równolegle połączonych ze sobą programowalnych elementów obliczeniowych MLP, zapewniającymi najwyższą w tej branży gęstość obliczeniową. MLP to wysoce konfigurowalne bloki obliczeniowe (przetwarzania intensywnego), obsługujące formaty od 4 do 24 bitów, wspierane przez wydajne tryby zmiennoprzecinkowe. Znajdziemy tu też bezpośrednie wsparcie dla 16-bitowego formatu TensorFlow, a także format zmiennoprzecinkowy bloku doładowanego, który podwaja liczbę silników obliczeniowych MLP.

MLP są ściśle sprzężone z wbudowanymi blokami pamięci, eliminując tradycyjne opóźnienia związane z routingiem FPGA. Zapewnia to dostarczanie danych do MLP z maksymalną wydajnością przy 750 MHz. To połączenie wysokiej gęstości obliczeniowej i wysokiej przepustowości zapewnia najwyższą użyteczność operacji na sekundę (Tops), spośród zbliżonych układów tego typu.

Światowa przepustowość

Krytyczne dla uczenia się maszynowego i wysoce wydajnych systemów obliczeniowych, jest osiąganie dużej przepustowości do pamięci poza układem, w celu budowania źródeł danych i buforów. Speedster 7t są pierwszymi i jedynymi układami na rynku, wspierającymi interfejs GDDR6, oferując najwyższą na rynku przepustowość do pamięci zewnętrznych.

Każdy z wbudowanych kontrolerów GDDR6 umożliwia transfer na poziomie 512 Gbps, a w układzie Speedster mamy ich osiem. Pozwala to na osiąganie łącznej przepustowości na poziomie 4 Tbps. Jest to równoważność przepustowości systemów HBM, lecz dużo niższym kosztem.

Wsparcie GDDR6 to nie jedyna przewaga tych układów w sferze przepustowości. W strukturze Speedster 7t zawarto 72 najwyższej klasy SerDes, które obsługiwać mają prędkości od 1 do 122 Gbps. Są tu też wspomniane układy MAC Ethernet 400G z korekcją błędów FEC (wspierające konfiguracje 4x 100G lub 8x 50 G), a także kontrolery PCI Express Gen5 (8- i 16-liniowe).

Wydajność transferowa

Wspomniane elementy i parametry przytłoczyłyby klasyczne routingi FPGA. Z tego też względu Speedster 7t zawiera nowoczesny, innowacyjny, szerokopasmowy i dwukierunkowy NoC 2D, rozciągający się w dwóch płaszczyznach na strukturze FPGA, łącząc się ze wszystkimi jego elementami, interfejsami, itp. Działa niczym sieć autostrad nad miejskim systemem szybkich połączeń.

Każdy wiersz i kolumna NoC zaimplementowana jest jako podwójne jednokierunkowe, 256-bitowe kanały AXI, działające na paśmie 2 GHz, dostarczając przepustowość na poziomie 512 Gbps w każdym kierunku, równocześnie. Uproszcza to tym samym superszybkie przesyłanie danych wewnątrz układu, zapewniając łatwe kierowanie strumieni danych do dowolnych, nawet niestandardowych silników przetwarzających. NoC ponadto ma za zadanie wyeliminować jakiekolwiek wąskie gardła w systemie łączeniowym, występujące w klasycznych konstrukcjach FPGA (korzystające z programowalnego routingi i tablic LUT). Rozwiązanie to też znacząco wpływa na redukcję zużycia energii.

A bezpieczeństwo?

Speedster 7t wspierać ma najnowocześniejsze funkcje zabezpieczające bitstream z wieloma warstwami obronnymi, zapewniając wysoki stopień ochrony poufnych danych oraz chroniąc integralność strumienia bitów. Jak podają twórcy, układom tym nie straszne jakiekolwiek ataki.

Klucze są szyfrowane w oparciu o funkcje PUF odporne na manipulacje fizyczne. Strumienie bitów są szyfrowane i uwierzytelniane za pomocą 256-bitowego AES-GCM. Strumienie bitów są dodatkowo dzielone na specjalne segmenty, by uchronić się przed atakami boczno-kanałowymi. Każdy segment prowadzony jest osobnymi kluczami. System deszyfrowania z kolei wykorzystuje różnicową analizę mocy (DPA). Klucz publiczny RSA jest uwierzytelniany za pomocą dedykowanego protokołu 2048-bitowego.

Wszechstronność i wygoda

Firma Achronix oferuje zarówno samodzielne układy FPGA, jak również systemy IP FPGA Speedcore, a które oparte są na tych samych technologiach. Pozwala to na płynną konwersję z Speedster 7t FPGA na ASIC.

Aplikacje FPGA zazwyczaj mają funkcje, które muszą pozostać programowalne, podczas gdy inne pozostać mogą stałymi funkcjami dedykowanymi konkretnej aplikacji systemowej. W przypadku konwersji ASIC stałe funkcje mogą zostać przeniesione w formę sprzętowej struktury ASIC, co zmniejsza rozmiar matrycy, koszt i moc. Klienci mogą spodziewać się redukcji mocy nawet o 50 procent i obniżenia kosztów o 90 procent, gdy wykorzystają Speedcore eFPGA IP do konwersji FPGA Speedster7t na dedykowane układy ASIC, pod konkretne, ostateczne projekty aplikacji.

Dostępność

Układy FPGA Speedster 7t mają być oferowane w wariantach od 363 k do 2.6 M jednostek obliczeniowych, 6-wejściowych LUT. Narzędzia wspomagające projektowanie (ACE), zawierające wsparcie dla Speedster FPGA i Speedcore eFPGA, są już dostępne.

Na pierwsze układy z nowej rodziny przyjdzie nam poczekać do czwartego kwartału 2019. Podobnie rzecz się ma z płytkami deweloperskimi.

© Achronix

Optymalizacja pod wydajność obliczeniową

Sercem Speedster 7t ma być masowa sieć równolegle połączonych ze sobą programowalnych elementów obliczeniowych MLP, zapewniającymi najwyższą w tej branży gęstość obliczeniową. MLP to wysoce konfigurowalne bloki obliczeniowe (przetwarzania intensywnego), obsługujące formaty od 4 do 24 bitów, wspierane przez wydajne tryby zmiennoprzecinkowe. Znajdziemy tu też bezpośrednie wsparcie dla 16-bitowego formatu TensorFlow, a także format zmiennoprzecinkowy bloku doładowanego, który podwaja liczbę silników obliczeniowych MLP.

MLP są ściśle sprzężone z wbudowanymi blokami pamięci, eliminując tradycyjne opóźnienia związane z routingiem FPGA. Zapewnia to dostarczanie danych do MLP z maksymalną wydajnością przy 750 MHz. To połączenie wysokiej gęstości obliczeniowej i wysokiej przepustowości zapewnia najwyższą użyteczność operacji na sekundę (Tops), spośród zbliżonych układów tego typu.

Światowa przepustowość

Krytyczne dla uczenia się maszynowego i wysoce wydajnych systemów obliczeniowych, jest osiąganie dużej przepustowości do pamięci poza układem, w celu budowania źródeł danych i buforów. Speedster 7t są pierwszymi i jedynymi układami na rynku, wspierającymi interfejs GDDR6, oferując najwyższą na rynku przepustowość do pamięci zewnętrznych.

Każdy z wbudowanych kontrolerów GDDR6 umożliwia transfer na poziomie 512 Gbps, a w układzie Speedster mamy ich osiem. Pozwala to na osiąganie łącznej przepustowości na poziomie 4 Tbps. Jest to równoważność przepustowości systemów HBM, lecz dużo niższym kosztem.

Wsparcie GDDR6 to nie jedyna przewaga tych układów w sferze przepustowości. W strukturze Speedster 7t zawarto 72 najwyższej klasy SerDes, które obsługiwać mają prędkości od 1 do 122 Gbps. Są tu też wspomniane układy MAC Ethernet 400G z korekcją błędów FEC (wspierające konfiguracje 4x 100G lub 8x 50 G), a także kontrolery PCI Express Gen5 (8- i 16-liniowe).

Wydajność transferowa

Wspomniane elementy i parametry przytłoczyłyby klasyczne routingi FPGA. Z tego też względu Speedster 7t zawiera nowoczesny, innowacyjny, szerokopasmowy i dwukierunkowy NoC 2D, rozciągający się w dwóch płaszczyznach na strukturze FPGA, łącząc się ze wszystkimi jego elementami, interfejsami, itp. Działa niczym sieć autostrad nad miejskim systemem szybkich połączeń.

Każdy wiersz i kolumna NoC zaimplementowana jest jako podwójne jednokierunkowe, 256-bitowe kanały AXI, działające na paśmie 2 GHz, dostarczając przepustowość na poziomie 512 Gbps w każdym kierunku, równocześnie. Uproszcza to tym samym superszybkie przesyłanie danych wewnątrz układu, zapewniając łatwe kierowanie strumieni danych do dowolnych, nawet niestandardowych silników przetwarzających. NoC ponadto ma za zadanie wyeliminować jakiekolwiek wąskie gardła w systemie łączeniowym, występujące w klasycznych konstrukcjach FPGA (korzystające z programowalnego routingi i tablic LUT). Rozwiązanie to też znacząco wpływa na redukcję zużycia energii.

A bezpieczeństwo?

Speedster 7t wspierać ma najnowocześniejsze funkcje zabezpieczające bitstream z wieloma warstwami obronnymi, zapewniając wysoki stopień ochrony poufnych danych oraz chroniąc integralność strumienia bitów. Jak podają twórcy, układom tym nie straszne jakiekolwiek ataki.

Klucze są szyfrowane w oparciu o funkcje PUF odporne na manipulacje fizyczne. Strumienie bitów są szyfrowane i uwierzytelniane za pomocą 256-bitowego AES-GCM. Strumienie bitów są dodatkowo dzielone na specjalne segmenty, by uchronić się przed atakami boczno-kanałowymi. Każdy segment prowadzony jest osobnymi kluczami. System deszyfrowania z kolei wykorzystuje różnicową analizę mocy (DPA). Klucz publiczny RSA jest uwierzytelniany za pomocą dedykowanego protokołu 2048-bitowego.

Wszechstronność i wygoda

Firma Achronix oferuje zarówno samodzielne układy FPGA, jak również systemy IP FPGA Speedcore, a które oparte są na tych samych technologiach. Pozwala to na płynną konwersję z Speedster 7t FPGA na ASIC.

Aplikacje FPGA zazwyczaj mają funkcje, które muszą pozostać programowalne, podczas gdy inne pozostać mogą stałymi funkcjami dedykowanymi konkretnej aplikacji systemowej. W przypadku konwersji ASIC stałe funkcje mogą zostać przeniesione w formę sprzętowej struktury ASIC, co zmniejsza rozmiar matrycy, koszt i moc. Klienci mogą spodziewać się redukcji mocy nawet o 50 procent i obniżenia kosztów o 90 procent, gdy wykorzystają Speedcore eFPGA IP do konwersji FPGA Speedster7t na dedykowane układy ASIC, pod konkretne, ostateczne projekty aplikacji.

Dostępność

Układy FPGA Speedster 7t mają być oferowane w wariantach od 363 k do 2.6 M jednostek obliczeniowych, 6-wejściowych LUT. Narzędzia wspomagające projektowanie (ACE), zawierające wsparcie dla Speedster FPGA i Speedcore eFPGA, są już dostępne.

Na pierwsze układy z nowej rodziny przyjdzie nam poczekać do czwartego kwartału 2019. Podobnie rzecz się ma z płytkami deweloperskimi.

© Achronix

Optymalizacja pod wydajność obliczeniową

Sercem Speedster 7t ma być masowa sieć równolegle połączonych ze sobą programowalnych elementów obliczeniowych MLP, zapewniającymi najwyższą w tej branży gęstość obliczeniową. MLP to wysoce konfigurowalne bloki obliczeniowe (przetwarzania intensywnego), obsługujące formaty od 4 do 24 bitów, wspierane przez wydajne tryby zmiennoprzecinkowe. Znajdziemy tu też bezpośrednie wsparcie dla 16-bitowego formatu TensorFlow, a także format zmiennoprzecinkowy bloku doładowanego, który podwaja liczbę silników obliczeniowych MLP.

MLP są ściśle sprzężone z wbudowanymi blokami pamięci, eliminując tradycyjne opóźnienia związane z routingiem FPGA. Zapewnia to dostarczanie danych do MLP z maksymalną wydajnością przy 750 MHz. To połączenie wysokiej gęstości obliczeniowej i wysokiej przepustowości zapewnia najwyższą użyteczność operacji na sekundę (Tops), spośród zbliżonych układów tego typu.

Światowa przepustowość

Krytyczne dla uczenia się maszynowego i wysoce wydajnych systemów obliczeniowych, jest osiąganie dużej przepustowości do pamięci poza układem, w celu budowania źródeł danych i buforów. Speedster 7t są pierwszymi i jedynymi układami na rynku, wspierającymi interfejs GDDR6, oferując najwyższą na rynku przepustowość do pamięci zewnętrznych.

Każdy z wbudowanych kontrolerów GDDR6 umożliwia transfer na poziomie 512 Gbps, a w układzie Speedster mamy ich osiem. Pozwala to na osiąganie łącznej przepustowości na poziomie 4 Tbps. Jest to równoważność przepustowości systemów HBM, lecz dużo niższym kosztem.

Wsparcie GDDR6 to nie jedyna przewaga tych układów w sferze przepustowości. W strukturze Speedster 7t zawarto 72 najwyższej klasy SerDes, które obsługiwać mają prędkości od 1 do 122 Gbps. Są tu też wspomniane układy MAC Ethernet 400G z korekcją błędów FEC (wspierające konfiguracje 4x 100G lub 8x 50 G), a także kontrolery PCI Express Gen5 (8- i 16-liniowe).

Wydajność transferowa

Wspomniane elementy i parametry przytłoczyłyby klasyczne routingi FPGA. Z tego też względu Speedster 7t zawiera nowoczesny, innowacyjny, szerokopasmowy i dwukierunkowy NoC 2D, rozciągający się w dwóch płaszczyznach na strukturze FPGA, łącząc się ze wszystkimi jego elementami, interfejsami, itp. Działa niczym sieć autostrad nad miejskim systemem szybkich połączeń.

Każdy wiersz i kolumna NoC zaimplementowana jest jako podwójne jednokierunkowe, 256-bitowe kanały AXI, działające na paśmie 2 GHz, dostarczając przepustowość na poziomie 512 Gbps w każdym kierunku, równocześnie. Uproszcza to tym samym superszybkie przesyłanie danych wewnątrz układu, zapewniając łatwe kierowanie strumieni danych do dowolnych, nawet niestandardowych silników przetwarzających. NoC ponadto ma za zadanie wyeliminować jakiekolwiek wąskie gardła w systemie łączeniowym, występujące w klasycznych konstrukcjach FPGA (korzystające z programowalnego routingi i tablic LUT). Rozwiązanie to też znacząco wpływa na redukcję zużycia energii.

A bezpieczeństwo?

Speedster 7t wspierać ma najnowocześniejsze funkcje zabezpieczające bitstream z wieloma warstwami obronnymi, zapewniając wysoki stopień ochrony poufnych danych oraz chroniąc integralność strumienia bitów. Jak podają twórcy, układom tym nie straszne jakiekolwiek ataki.

Klucze są szyfrowane w oparciu o funkcje PUF odporne na manipulacje fizyczne. Strumienie bitów są szyfrowane i uwierzytelniane za pomocą 256-bitowego AES-GCM. Strumienie bitów są dodatkowo dzielone na specjalne segmenty, by uchronić się przed atakami boczno-kanałowymi. Każdy segment prowadzony jest osobnymi kluczami. System deszyfrowania z kolei wykorzystuje różnicową analizę mocy (DPA). Klucz publiczny RSA jest uwierzytelniany za pomocą dedykowanego protokołu 2048-bitowego.

Wszechstronność i wygoda

Firma Achronix oferuje zarówno samodzielne układy FPGA, jak również systemy IP FPGA Speedcore, a które oparte są na tych samych technologiach. Pozwala to na płynną konwersję z Speedster 7t FPGA na ASIC.

Aplikacje FPGA zazwyczaj mają funkcje, które muszą pozostać programowalne, podczas gdy inne pozostać mogą stałymi funkcjami dedykowanymi konkretnej aplikacji systemowej. W przypadku konwersji ASIC stałe funkcje mogą zostać przeniesione w formę sprzętowej struktury ASIC, co zmniejsza rozmiar matrycy, koszt i moc. Klienci mogą spodziewać się redukcji mocy nawet o 50 procent i obniżenia kosztów o 90 procent, gdy wykorzystają Speedcore eFPGA IP do konwersji FPGA Speedster7t na dedykowane układy ASIC, pod konkretne, ostateczne projekty aplikacji.

Dostępność

Układy FPGA Speedster 7t mają być oferowane w wariantach od 363 k do 2.6 M jednostek obliczeniowych, 6-wejściowych LUT. Narzędzia wspomagające projektowanie (ACE), zawierające wsparcie dla Speedster FPGA i Speedcore eFPGA, są już dostępne.

Na pierwsze układy z nowej rodziny przyjdzie nam poczekać do czwartego kwartału 2019. Podobnie rzecz się ma z płytkami deweloperskimi.