© Aspinity

Technologie |

Rewolucja analogowa od Aspinity

W dzisiejszym świecie opanowanym przez smartfony, technologie ubierane, Przemysł 4.0 i internet przedmiotów (IoT) stale wzrasta zapotrzebowanie na wydajne, energooszczędne i tanie czujniki.

Niezależnie od tego, czy użyte sensory umożliwiają sterowanie głosowe, śledzenie stanu zdrowia czy tworzenie interfejsów użytkownika następnej generacji, konieczne jest przetwarzanie dużej ilości danych. Obecne urządzenia muszą sprawnie zarządzać tą ogromną ilością informacji a przy tym być energooszczędne i tanie. Z pomocą przychodzi nowa technologia przetwarzania analogowego opracowana przez firmę Aspinity.

Rewolucyjne rozwiązanie Aspinity umożliwia konwersję danych w czujniku w najbardziej naturalnej postaci, czyli analogowej. Wyodrębniając istotne cechy aplikacji przed digitalizacją danych z czujników, Aspinity przenosi analizę danych na przód łańcucha przetwarzania sygnałów. Przykłady obejmują: aktywację cyfrowego rozpoznawania mowy przy pomocy analogowego detektora głosu wysokiej jakości, analizę analogową stanu wibracji w urządzeniach do monitorowania maszyn przemysłowych czy monitorowanie rytmu serca za pomocą analizy sygnałów EKG i PPG (sygnał fotopletyzmograficzny). We wszystkich tych przykładach wydajna przed-cyfrowa analiza danych pozwala na znaczną redukcję zużycia energii urządzenia oraz zmniejsza koszty ogólne. Analiza danych analogowych jest możliwa dzięki osiągniętym innowacjom Aspinity w programowaniu analogowym i opracowywaniu algorytmów analogowych. Mogą być szybko zaimplementowane w układach przyczyniając się do szybkiego powstania szeregu nowych produktów lub aktualizując już powstałe. Portfolio firmy Aspinity zawiera wydajne algorytmy analogowe, które pasują do najnowocześniejszych obecnie algorytmów cyfrowych.

Architektura RAMP

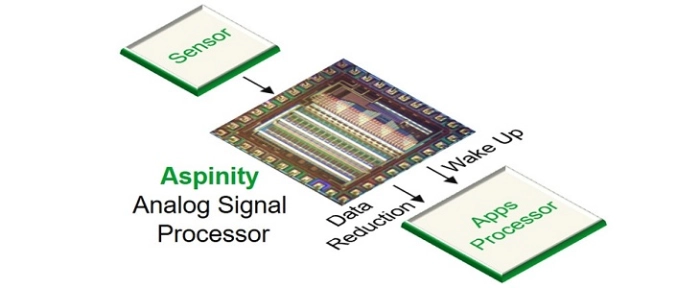

Podobnie jak w pełni cyfrowo programowalne układy FPGA, które umożliwiły szybkie prototypowanie systemów cyfrowych, analogowe układy programowalne FPAA (Field-Programmable Analog Array) starają się zapewnić taką samą elastyczność i możliwość rekonfiguracji w projektach analogowych. Rezultatem jest pojedynczy układ scalony, który może implementować różnorodne systemy przetwarzania sygnału analogowego, określone przez projektanta. Sercem rozwiązania Aspinity jest skalowalny, z programowalnym przetwornikiem sygnału ASP (Analog Signal Processing) procesor RAMP (Reconfigurable Analog/Mixed-Signal Processor), który może obsługiwać zaawansowane algorytmy analizy danych dla wielu aplikacji. Architektura RAMP umożliwia odwzorowanie cyfrowego przetwarzania sygnału w formacie analogowym, dzięki czemu możliwe jest dokładniejsze przetwarzanie danych przy znacznie mniejszym poborze mocy.

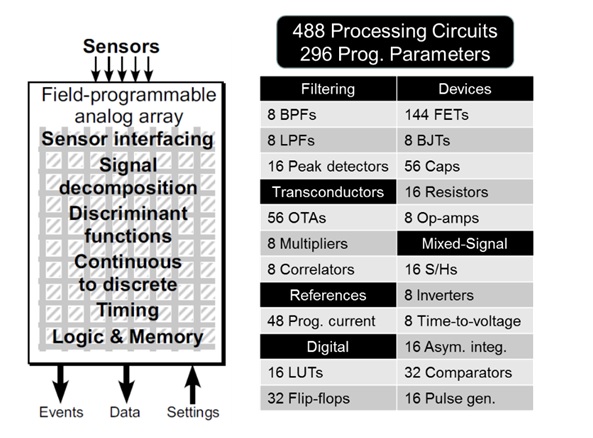

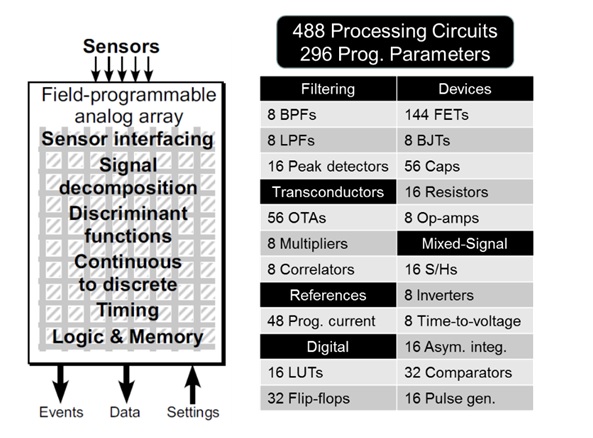

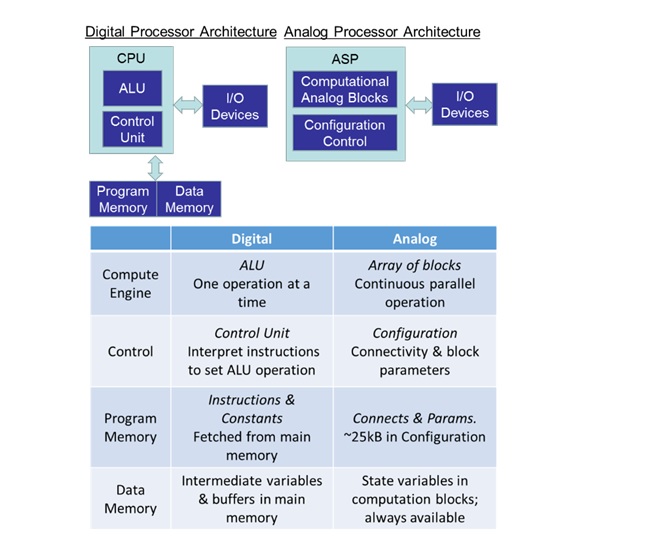

Rysunek 1. Architektura RAMP oraz lista elementów cyfrowych

Innowacja Aspinity polega na wykorzystaniu charakterystyk pracy wielkosygnałowej małej liczby tranzystorów, tak aby stworzyć architekturę modułowych, równoległych i działających w sposób ciągły bloków analogowych, które można skonfigurować w celu połączenia z czujnikami, przetwarzania sygnałów i podejmowania decyzji. Każdy z tych bloków - CAB (Configurable Analog Block) i CLB (Configurable Logic Block), umieszczony jest w znacznie mniejszej przestrzeni niż tradycyjny blok analogowy, dzięki czemu redukuje problemy związane z digitalizacją danych z czujników analogowych, wykorzystywanych do przetwarzania cyfrowego. Nowa architektura pozwala obniżyć moc całego systemu o rząd wielkości, umożliwiając stałe przetwarzanie danych analogowych, z dużo większą dokładnością i niższym kosztem, niż obecnie stosowane rozwiązania cyfrowego przetwarzania.

Układ RAMP

Aspinity doprowadziło do wdrożenia swojego rozwiązania w krzemie, wprowadzając na rynek programowalny układ scalony RAMP o niewielkich wymiarach 5x5mm. Układ ten zawiera złożone obwody o topologii analogowo-centrycznej, które mogą być skonfigurowane (zaprogramowane) automatycznie dla określonej aplikacji. Obecne metody projektowania analogowych/mieszanych sygnałów wymagają złożonego podejścia i dużego wysiłku przy ich wdrażaniu. Układ RAMP to krzemowe urządzenie gotowe do wdrożenia, które można szybko zaprogramować (i przeprogramować), tak aby ostatecznie obniżyć koszt i czas realizacji projektu analogowego i mieszanego. RAMP może być użyty jako inteligentne urządzenie do "budzenia" lub zastąpić kompletny system do cyfrowego przetwarzania danych.

Rysunek 1. Architektura RAMP oraz lista elementów cyfrowych

Innowacja Aspinity polega na wykorzystaniu charakterystyk pracy wielkosygnałowej małej liczby tranzystorów, tak aby stworzyć architekturę modułowych, równoległych i działających w sposób ciągły bloków analogowych, które można skonfigurować w celu połączenia z czujnikami, przetwarzania sygnałów i podejmowania decyzji. Każdy z tych bloków - CAB (Configurable Analog Block) i CLB (Configurable Logic Block), umieszczony jest w znacznie mniejszej przestrzeni niż tradycyjny blok analogowy, dzięki czemu redukuje problemy związane z digitalizacją danych z czujników analogowych, wykorzystywanych do przetwarzania cyfrowego. Nowa architektura pozwala obniżyć moc całego systemu o rząd wielkości, umożliwiając stałe przetwarzanie danych analogowych, z dużo większą dokładnością i niższym kosztem, niż obecnie stosowane rozwiązania cyfrowego przetwarzania.

Układ RAMP

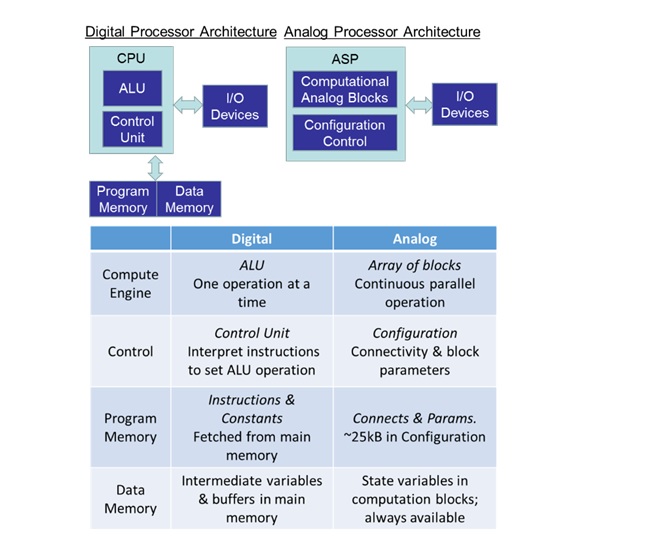

Aspinity doprowadziło do wdrożenia swojego rozwiązania w krzemie, wprowadzając na rynek programowalny układ scalony RAMP o niewielkich wymiarach 5x5mm. Układ ten zawiera złożone obwody o topologii analogowo-centrycznej, które mogą być skonfigurowane (zaprogramowane) automatycznie dla określonej aplikacji. Obecne metody projektowania analogowych/mieszanych sygnałów wymagają złożonego podejścia i dużego wysiłku przy ich wdrażaniu. Układ RAMP to krzemowe urządzenie gotowe do wdrożenia, które można szybko zaprogramować (i przeprogramować), tak aby ostatecznie obniżyć koszt i czas realizacji projektu analogowego i mieszanego. RAMP może być użyty jako inteligentne urządzenie do "budzenia" lub zastąpić kompletny system do cyfrowego przetwarzania danych.  Rysunek 3. Porównanie architektury cyfrowej i analogowej

Środowisko programistyczne i ewaluacyjne

Firma Aspinity dostarcza płytę ewaluacyjną oraz środowisko programistyczne do oprogramowania układu RAMP. Zastosowana metodologia umożliwia programistom wykonanie trzech zadań programistycznych omówionych wcześniej, w tym wyboru i złożenia konfigurowalnych bloków funkcjonalnych. Dzięki temu możliwe jest szybkie prototypowanie w aplikacjach, które posiadają już warstwę sprzętową a twórcom aplikacji poznanie poziomu implementacji w systemie przy użyciu końcowych algorytmów. Płyta posiada wiele typów wejść dla różnych czujników, mikrokontroler i inne interfejsy.

Rysunek 3. Porównanie architektury cyfrowej i analogowej

Środowisko programistyczne i ewaluacyjne

Firma Aspinity dostarcza płytę ewaluacyjną oraz środowisko programistyczne do oprogramowania układu RAMP. Zastosowana metodologia umożliwia programistom wykonanie trzech zadań programistycznych omówionych wcześniej, w tym wyboru i złożenia konfigurowalnych bloków funkcjonalnych. Dzięki temu możliwe jest szybkie prototypowanie w aplikacjach, które posiadają już warstwę sprzętową a twórcom aplikacji poznanie poziomu implementacji w systemie przy użyciu końcowych algorytmów. Płyta posiada wiele typów wejść dla różnych czujników, mikrokontroler i inne interfejsy.

Rysunek 1. Architektura RAMP oraz lista elementów cyfrowych

Innowacja Aspinity polega na wykorzystaniu charakterystyk pracy wielkosygnałowej małej liczby tranzystorów, tak aby stworzyć architekturę modułowych, równoległych i działających w sposób ciągły bloków analogowych, które można skonfigurować w celu połączenia z czujnikami, przetwarzania sygnałów i podejmowania decyzji. Każdy z tych bloków - CAB (Configurable Analog Block) i CLB (Configurable Logic Block), umieszczony jest w znacznie mniejszej przestrzeni niż tradycyjny blok analogowy, dzięki czemu redukuje problemy związane z digitalizacją danych z czujników analogowych, wykorzystywanych do przetwarzania cyfrowego. Nowa architektura pozwala obniżyć moc całego systemu o rząd wielkości, umożliwiając stałe przetwarzanie danych analogowych, z dużo większą dokładnością i niższym kosztem, niż obecnie stosowane rozwiązania cyfrowego przetwarzania.

Układ RAMP

Aspinity doprowadziło do wdrożenia swojego rozwiązania w krzemie, wprowadzając na rynek programowalny układ scalony RAMP o niewielkich wymiarach 5x5mm. Układ ten zawiera złożone obwody o topologii analogowo-centrycznej, które mogą być skonfigurowane (zaprogramowane) automatycznie dla określonej aplikacji. Obecne metody projektowania analogowych/mieszanych sygnałów wymagają złożonego podejścia i dużego wysiłku przy ich wdrażaniu. Układ RAMP to krzemowe urządzenie gotowe do wdrożenia, które można szybko zaprogramować (i przeprogramować), tak aby ostatecznie obniżyć koszt i czas realizacji projektu analogowego i mieszanego. RAMP może być użyty jako inteligentne urządzenie do "budzenia" lub zastąpić kompletny system do cyfrowego przetwarzania danych.

Rysunek 1. Architektura RAMP oraz lista elementów cyfrowych

Innowacja Aspinity polega na wykorzystaniu charakterystyk pracy wielkosygnałowej małej liczby tranzystorów, tak aby stworzyć architekturę modułowych, równoległych i działających w sposób ciągły bloków analogowych, które można skonfigurować w celu połączenia z czujnikami, przetwarzania sygnałów i podejmowania decyzji. Każdy z tych bloków - CAB (Configurable Analog Block) i CLB (Configurable Logic Block), umieszczony jest w znacznie mniejszej przestrzeni niż tradycyjny blok analogowy, dzięki czemu redukuje problemy związane z digitalizacją danych z czujników analogowych, wykorzystywanych do przetwarzania cyfrowego. Nowa architektura pozwala obniżyć moc całego systemu o rząd wielkości, umożliwiając stałe przetwarzanie danych analogowych, z dużo większą dokładnością i niższym kosztem, niż obecnie stosowane rozwiązania cyfrowego przetwarzania.

Układ RAMP

Aspinity doprowadziło do wdrożenia swojego rozwiązania w krzemie, wprowadzając na rynek programowalny układ scalony RAMP o niewielkich wymiarach 5x5mm. Układ ten zawiera złożone obwody o topologii analogowo-centrycznej, które mogą być skonfigurowane (zaprogramowane) automatycznie dla określonej aplikacji. Obecne metody projektowania analogowych/mieszanych sygnałów wymagają złożonego podejścia i dużego wysiłku przy ich wdrażaniu. Układ RAMP to krzemowe urządzenie gotowe do wdrożenia, które można szybko zaprogramować (i przeprogramować), tak aby ostatecznie obniżyć koszt i czas realizacji projektu analogowego i mieszanego. RAMP może być użyty jako inteligentne urządzenie do "budzenia" lub zastąpić kompletny system do cyfrowego przetwarzania danych. Ponieważ RAMP jest analogową implementacją, nie wymaga zegara ani pamięci, jak w przypadku wdrożeń cyfrowych. Zużywa jedynie około 10 µA podczas pracy ciągłej. Układ wykonany jest w standardowej technologii wytwarzania CMOS 0.35µm bez wariantów procesowych lub dostosowań technologii, tak jak ma to miejsce w przypadku innych technologii analogowych. Programowanie układu RAMP Chociaż architektury procesorów cyfrowych znacznie różnią się od architektury procesora analogowego Aspinity, to jednak proces programowania jest podobny. Programowanie RAMP obejmuje 3 podstawowe elementy: konfigurację, programowanie i kalibrację - w oddzielnym algorytmie, który można załadować za pomocą prostego interfejsu szeregowego. Po pierwsze, bloki funkcjonalne/obwody przetwarzania potrzebne dla aplikacji są "konfigurowane" za pomocą struktury przełączającej. Następnie, w zależności od wybranych bloków funkcjonalnych i wymagań aplikacji, każdy blok jest "zaprogramowany" za pomocą zestawu parametrów, które umożliwiają określonym blokom dokładne wykonywanie ich zadań w łańcuchu przetwarzania sygnałów. Wreszcie, ze względu na złożoną naturę obwodów analogowych i różnice w procesach technologicznych, stosuje się "kalibrację" w celu rozwiązania problemów związanych z niespójnością w konkretnych blokach. Wynikowy algorytm może być modyfikowany i ładowany do RAMP wiele razy, nawet w już wdrożonym środowisku.Rysunek 2. Rdzeń układu RAMP

Rysunek 3. Porównanie architektury cyfrowej i analogowej

Środowisko programistyczne i ewaluacyjne

Firma Aspinity dostarcza płytę ewaluacyjną oraz środowisko programistyczne do oprogramowania układu RAMP. Zastosowana metodologia umożliwia programistom wykonanie trzech zadań programistycznych omówionych wcześniej, w tym wyboru i złożenia konfigurowalnych bloków funkcjonalnych. Dzięki temu możliwe jest szybkie prototypowanie w aplikacjach, które posiadają już warstwę sprzętową a twórcom aplikacji poznanie poziomu implementacji w systemie przy użyciu końcowych algorytmów. Płyta posiada wiele typów wejść dla różnych czujników, mikrokontroler i inne interfejsy.

Rysunek 3. Porównanie architektury cyfrowej i analogowej

Środowisko programistyczne i ewaluacyjne

Firma Aspinity dostarcza płytę ewaluacyjną oraz środowisko programistyczne do oprogramowania układu RAMP. Zastosowana metodologia umożliwia programistom wykonanie trzech zadań programistycznych omówionych wcześniej, w tym wyboru i złożenia konfigurowalnych bloków funkcjonalnych. Dzięki temu możliwe jest szybkie prototypowanie w aplikacjach, które posiadają już warstwę sprzętową a twórcom aplikacji poznanie poziomu implementacji w systemie przy użyciu końcowych algorytmów. Płyta posiada wiele typów wejść dla różnych czujników, mikrokontroler i inne interfejsy.

Wraz z ogromnym wzrostem ilości czujników i urządzeń brzegowych wzrasta obciążenie sieci i zapotrzebowanie na energię. Spowodowane jest to transferem danych do urządzeń, które przetwarzają i analizują otrzymane informacje. Aspinity poprzez układ RAMP rozwiązuje te problemy, wykonując wiele tradycyjnych zadań przetwarzania cyfrowego w domenie analogowej. W rezultacie analiza danych i ich redukcja może być zrealizowana na „brzegu” czujnika w naturalnej - analogowej domenie danych czujnika. W konsekwencji, zmniejsza się zużycie energii poprzez ograniczenie cyfryzacji danych z czujników tylko do danych istotnych dla aplikacji. Innowacje Aspinity w przetwarzaniu sygnału analogowego pozwolą na powstanie nowych architektur i systemów oraz zainicjują znaczącą zmianę przetwarzania danych w wieku urządzeń IoT. fot. © AspinityRysunek 4. Płyta ewaluacyjna RAMP1