© PIXABAY

Technologie |

Nowe energooszczędne pamięci IP SRAM

Budowa energooszczędnych systemów dla rynku urządzeń noszonych, czy Internetu rzeczy wymaga nowego podejścia w tworzeniu i weryfikowaniu pamięci SRAM.

Nowoczesne elektroniczne urządzenia konsumenckie w dużym stopniu wykorzystują wysoce zintegrowane elementy elektroniczne - powszechnie znane jako układy typu System-on-Chip (lub SoC). Statyczna pamięć o dostępie swobodnym - SRAM jest podstawowym składnikiem wszystkich SoC i jest często pojedynczym największym składnikiem pod względem powierzchni chipa. W wielu przypadkach zajmuje do 50% aktywnego obszaru w SoC. Obniżenie zużycia energii w urządzeniach jest obecnie celem do osiągnięcia przez projektantów elektroniki, w których głównym źródłem zasilania jest bateria. Jednym z ograniczeń do pokonania jest opracowanie takich typów pamięci SRAM, które zapewnią długą żywotność baterii i minimalne zużycie energii w trybie gotowości i uśpienia.

Firma SureCore, która jest producentem pamięci o ultra-niskim poborze mocy dla projektantów układów scalonych zaprezentowała dwie nowe rodziny produktów. Pierwsza – PowerMiser, to pamięć IP SRAM ogólnego zastosowania, zdolna do osiągnięcia ponad 50% dynamicznych i 20% statycznych oszczędności w poborze energii w porównaniu z standardowymi produktami na rynku. Została zrealizowana w obu procesach technologicznych 28nm FDSOI i 40nm ULP (Ultra Low Power) BULK CMOS. Opatentowane techniki "Bit Line Voltage Control" pozwoliły na wyeliminowanie zakłóceń w pracy dla niskich napięć roboczych.

Układ może teraz pracować w dodatkowych trybach uśpienia: lekkie uśpienie, umożliwiające szybkie wybudzenie oraz głębokie uśpienie, które maksymalnie ogranicza prądy upływu. Druga rodzina produktów – EverOn, to z kolei pamięć stworzona specjalnie dla rynku IoT i urządzeń noszonych. Wymaga niemal wartości progowej napięcia zasilania, umożliwiając do 80% oszczędności w dynamicznym poborze energii i do 75% redukcji mocy statycznej. Dzięki procesowi firmy TSMC obniżono prądy upływu o 70% a zużycie energii nawet o 30% w porównaniu z procesem Low Power (LP). Użyta technologia "SMART-Assist" umożliwia wydajne działanie aż do granicznego napięcia.

Dalsze innowacje architektoniczne obejmują podział pamięci na cztery banki, co w połączeniu z ulepszonymi trybami uśpienia zapewnia większą elastyczność systemu. Każdy bank może znajdować się niezależnie w trybie aktywnym, w trybie lekkiego lub głębokiego uśpienia, lub wyłączenia. Nowe tryby oszczędzania energii zapewniają większą elastyczność dostosowując wydajność produktu do aktualnych potrzeb, w ten sposób wydłużając żywotność baterii. Obie rodziny produktów oparto na standardowej architekturze komórek, co pozwoliło na wykorzystanie powszechnie znanych procesów wytwarzania układów pamięci. Dodatkowym kluczem do osiągnięcia wiodącej na rynku wysokiej energooszczędności jest kompleksowa strategia weryfikacji.

Weryfikacja jest integralną częścią każdego procesu rozwoju obwodów scalonych. Proces weryfikacji musi potwierdzić, że projekt spełnia określone kryteria wydajności w pełnym zakresie warunków pracy, przed jego przekazaniem do procesu produkcji. Ogólnie, proces obejmuje wykorzystanie abstrakcji (uproszczeń znacznie bardziej skomplikowanych procesów) w projekcie w odpowiedniej formie, na przykład: po procesie projektowania wygenerowanie netlisty i przeprowadzenie symulacji w celu sprawdzenia poprawności projektu. Proces weryfikacji musi uwzględniać wiele różnych aspektów wydajności, dlatego aby go zakończyć może okazać się konieczne użycie kilku różnych typów abstrakcji projektowych oraz narzędzi do symulacji. W przypadku pamięci SRAM jest to szczególnie ważne.

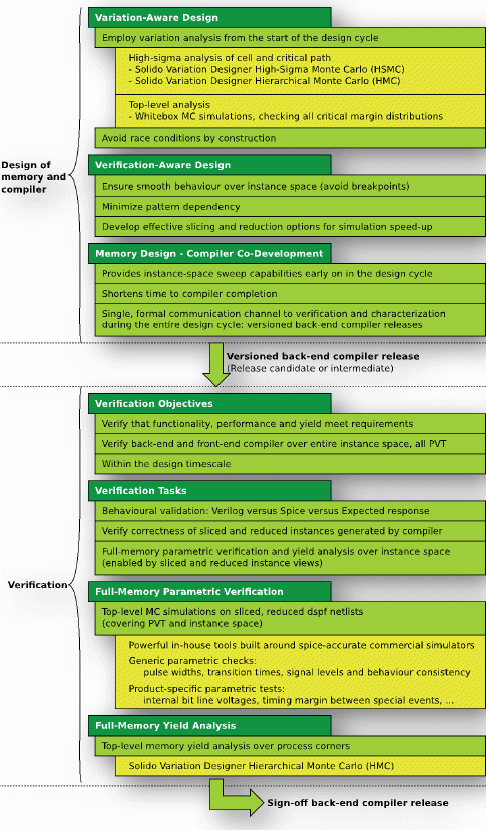

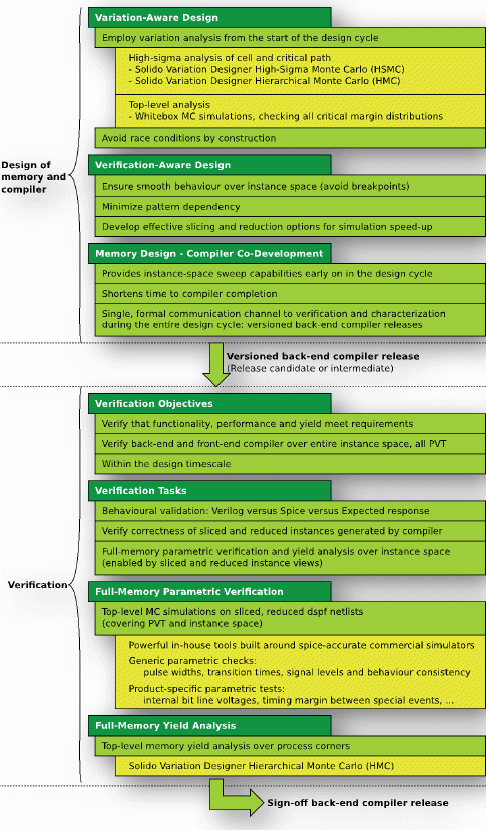

Weryfikacja kompletnej przestrzeni instancji kompilatora wymaga rozwiązania kilku unikalnych wyzwań. Obejmują one, ale nie są ograniczone do: (1) konieczności zmaksymalizowania zasięgu w całej przestrzeni instancji w zakresie kompilatora oraz (2) zdolności sprawdzania poprawności projektu i wydajności parametrów w stopniu wystarczającym dla zakresu PVT. Ważne jest zatem, aby weryfikacja SRAM opierała się na strategii uwzględniania różnic. Wyzwania te muszą być również brane po uwagę w czasie tworzenia projektu. Aby osiągnąć ten cel, całościowa weryfikacja jest podzielona na kilka unikalnych zadań

Weryfikacja kompletnej przestrzeni instancji kompilatora wymaga rozwiązania kilku unikalnych wyzwań. Obejmują one, ale nie są ograniczone do: (1) konieczności zmaksymalizowania zasięgu w całej przestrzeni instancji w zakresie kompilatora oraz (2) zdolności sprawdzania poprawności projektu i wydajności parametrów w stopniu wystarczającym dla zakresu PVT. Ważne jest zatem, aby weryfikacja SRAM opierała się na strategii uwzględniania różnic. Wyzwania te muszą być również brane po uwagę w czasie tworzenia projektu. Aby osiągnąć ten cel, całościowa weryfikacja jest podzielona na kilka unikalnych zadań

Źródło: © SureCore

Weryfikacja kompletnej przestrzeni instancji kompilatora wymaga rozwiązania kilku unikalnych wyzwań. Obejmują one, ale nie są ograniczone do: (1) konieczności zmaksymalizowania zasięgu w całej przestrzeni instancji w zakresie kompilatora oraz (2) zdolności sprawdzania poprawności projektu i wydajności parametrów w stopniu wystarczającym dla zakresu PVT. Ważne jest zatem, aby weryfikacja SRAM opierała się na strategii uwzględniania różnic. Wyzwania te muszą być również brane po uwagę w czasie tworzenia projektu. Aby osiągnąć ten cel, całościowa weryfikacja jest podzielona na kilka unikalnych zadań

Weryfikacja kompletnej przestrzeni instancji kompilatora wymaga rozwiązania kilku unikalnych wyzwań. Obejmują one, ale nie są ograniczone do: (1) konieczności zmaksymalizowania zasięgu w całej przestrzeni instancji w zakresie kompilatora oraz (2) zdolności sprawdzania poprawności projektu i wydajności parametrów w stopniu wystarczającym dla zakresu PVT. Ważne jest zatem, aby weryfikacja SRAM opierała się na strategii uwzględniania różnic. Wyzwania te muszą być również brane po uwagę w czasie tworzenia projektu. Aby osiągnąć ten cel, całościowa weryfikacja jest podzielona na kilka unikalnych zadań- weryfikacja modelu behawioralnego,

- pełna funkcjonalna weryfikacja trybu działania,

- uwzględnianie różnic w parametrach,

- sprawdzanie poprawności działania parametrów komórek na poziomie 6 sigma.

Źródło: © SureCore