© 4designersart dreamstime.com

Technologie |

Układy programowalne FPGA z otwartą architekturą RISC-V od Microsemi

Obecne technologie wykorzystywane w przemyśle półprzewodnikowym zostały już wykorzystane niemal do granic fizycznych, dzięki czemu nowe rozwiązania są kosztowne i trudne do wprowadzenia. Konieczne jest zatem zwrócenie się w kierunku całkiem nowej architektury układów.

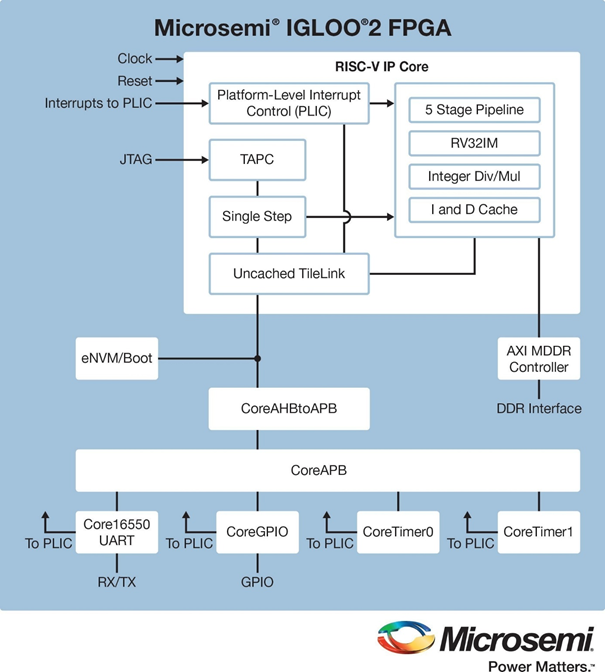

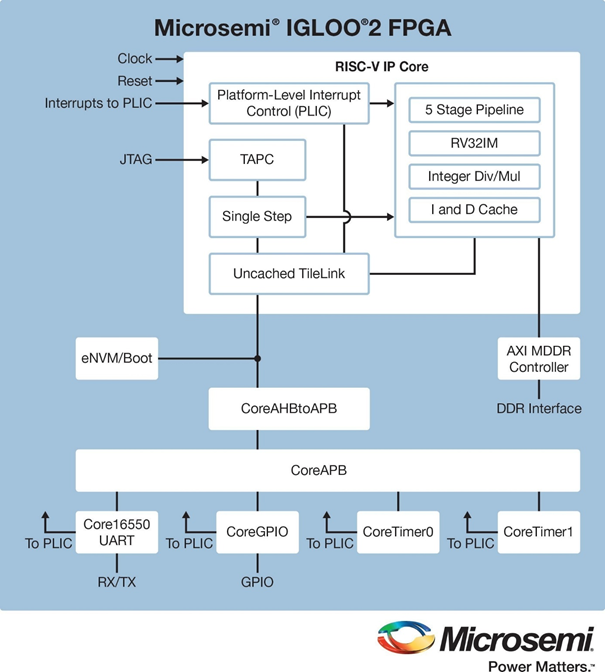

Firma Microsemi wiodący producent półprzewodników i systemowych rozwiązań przeznaczonych dla centrów przetwarzania danych, przemysłu obronnego i lotniczego, systemów łączności i bezpieczeństwa, wprowadził pierwszy układ programowalny FPGA o nowej - otwartej architekturze RISC-V. Rozwiązanie pod postacią rdzenia IP (Intellectual Property Core) zawiera pełny zestaw narzędzi programistycznych dla systemów wbudowanych.

RISC-V (wymawiane: „risk-five”) jest to nowy zestaw instrukcji architektury (ISA - Instruction Set Architecture), który bazuje na poprzednich zasadach architektury RISC (Reduced Instruction Set Computing). Powstający w ten sposób standard otwartej architektury wspierany jest również przez szereg firm, takich jak: Bluespec, Inc., Google, Hewlett Packard Enterprise, Lattice Semiconductor. Chociaż nie jest pierwszym rozwiązaniem typu otwartego, to na pewno znaczącym, ponieważ został zaprojektowany do stosowania w nowoczesnych urządzeniach: począwszy od centrów przetwarzania danych w chmurze, poprzez zaawansowane technologicznie telefony komórkowe, do najmniejszych systemów wbudowanych.

Opracowany rdzeń RV32IM oparty o RISC-V jest szczególnie atrakcyjny dla aplikacji związanych z bezpieczeństwem i ochroną danych, ponieważ przesłania międzyrejestrowe (RTL - Register Transfer Level) kodu źródłowego są możliwe do sprawdzenia. W ten sposób użytkownik może sprawdzić bezpieczeństwo samego procesora, co nie jest możliwe w innych układach posiadających zamkniętą architekturę. W zastosowaniach krytycznych dla pełnego bezpieczeństwa możliwe jest uruchomienie wielu rdzeni RISC-V, które zapewnią ciągłość działania takiego systemu, nawet w sytuacji jeżeli jeden z nich zawiedzie.

© Microsemi

Rdzeń RV32IM RISC-V został opracowany we współpracy z firmą SiFive, która stara się wprowadzić oprogramowanie typu „open source” do przemysłu półprzewodnikowego. Dzięki wspólnej pracy użytkownicy mają możliwość projektowania w otwartej ISA, umożliwiono również pełne i swobodne wykorzystanie oprogramowania w innych układach z RISC-V oraz stworzono bardziej bezpieczną architekturę procesora. Nigdy wcześniej procesor nie umożliwiał projektantom na sprawdzanie, modyfikowanie, adaptowanie, współpracę i przeniesienie swojego projektu do najlepszej platformy dla swoich produktów. Bezpieczne i energooszczędne układy FPGA z wbudowaną pamięcią flash idealnie pasują do tego określenia.

W przeciwieństwie do większości ISA, RISC-V jest dostępny bez ograniczeń dla wszystkich użytkowników, pozwalając im na projektowanie, produkcję i sprzedaż układów oraz oprogramowania.

RV32IM RISC-V zastosowano w układach FPGA z rodziny IGLOO2, SmartFusion2 system-on-chip (SoC) i RTG4, wraz z zintegrowanym środowiskiem programistycznym SoftConsole. Środowisko to jest darmowe, oparte na platformie Eclipse i zawiera w pełni zintegrowany debugger, który umożliwia łatwy dostęp do zawartości pamięci, rejestrów oraz na wykonanie pojedynczej instrukcji. Całość umieszczona jest na Linuxie, a dzięki specjalnemu zestawowi narzędzi programistycznych Libero SoC Design Suite producent zapewnia pełne wspomaganie projektowe.

© Microsemi

Rdzeń RV32IM RISC-V został opracowany we współpracy z firmą SiFive, która stara się wprowadzić oprogramowanie typu „open source” do przemysłu półprzewodnikowego. Dzięki wspólnej pracy użytkownicy mają możliwość projektowania w otwartej ISA, umożliwiono również pełne i swobodne wykorzystanie oprogramowania w innych układach z RISC-V oraz stworzono bardziej bezpieczną architekturę procesora. Nigdy wcześniej procesor nie umożliwiał projektantom na sprawdzanie, modyfikowanie, adaptowanie, współpracę i przeniesienie swojego projektu do najlepszej platformy dla swoich produktów. Bezpieczne i energooszczędne układy FPGA z wbudowaną pamięcią flash idealnie pasują do tego określenia.

W przeciwieństwie do większości ISA, RISC-V jest dostępny bez ograniczeń dla wszystkich użytkowników, pozwalając im na projektowanie, produkcję i sprzedaż układów oraz oprogramowania.

RV32IM RISC-V zastosowano w układach FPGA z rodziny IGLOO2, SmartFusion2 system-on-chip (SoC) i RTG4, wraz z zintegrowanym środowiskiem programistycznym SoftConsole. Środowisko to jest darmowe, oparte na platformie Eclipse i zawiera w pełni zintegrowany debugger, który umożliwia łatwy dostęp do zawartości pamięci, rejestrów oraz na wykonanie pojedynczej instrukcji. Całość umieszczona jest na Linuxie, a dzięki specjalnemu zestawowi narzędzi programistycznych Libero SoC Design Suite producent zapewnia pełne wspomaganie projektowe.

© Microsemi

Rdzeń RV32IM RISC-V został opracowany we współpracy z firmą SiFive, która stara się wprowadzić oprogramowanie typu „open source” do przemysłu półprzewodnikowego. Dzięki wspólnej pracy użytkownicy mają możliwość projektowania w otwartej ISA, umożliwiono również pełne i swobodne wykorzystanie oprogramowania w innych układach z RISC-V oraz stworzono bardziej bezpieczną architekturę procesora. Nigdy wcześniej procesor nie umożliwiał projektantom na sprawdzanie, modyfikowanie, adaptowanie, współpracę i przeniesienie swojego projektu do najlepszej platformy dla swoich produktów. Bezpieczne i energooszczędne układy FPGA z wbudowaną pamięcią flash idealnie pasują do tego określenia.

W przeciwieństwie do większości ISA, RISC-V jest dostępny bez ograniczeń dla wszystkich użytkowników, pozwalając im na projektowanie, produkcję i sprzedaż układów oraz oprogramowania.

RV32IM RISC-V zastosowano w układach FPGA z rodziny IGLOO2, SmartFusion2 system-on-chip (SoC) i RTG4, wraz z zintegrowanym środowiskiem programistycznym SoftConsole. Środowisko to jest darmowe, oparte na platformie Eclipse i zawiera w pełni zintegrowany debugger, który umożliwia łatwy dostęp do zawartości pamięci, rejestrów oraz na wykonanie pojedynczej instrukcji. Całość umieszczona jest na Linuxie, a dzięki specjalnemu zestawowi narzędzi programistycznych Libero SoC Design Suite producent zapewnia pełne wspomaganie projektowe.

© Microsemi

Rdzeń RV32IM RISC-V został opracowany we współpracy z firmą SiFive, która stara się wprowadzić oprogramowanie typu „open source” do przemysłu półprzewodnikowego. Dzięki wspólnej pracy użytkownicy mają możliwość projektowania w otwartej ISA, umożliwiono również pełne i swobodne wykorzystanie oprogramowania w innych układach z RISC-V oraz stworzono bardziej bezpieczną architekturę procesora. Nigdy wcześniej procesor nie umożliwiał projektantom na sprawdzanie, modyfikowanie, adaptowanie, współpracę i przeniesienie swojego projektu do najlepszej platformy dla swoich produktów. Bezpieczne i energooszczędne układy FPGA z wbudowaną pamięcią flash idealnie pasują do tego określenia.

W przeciwieństwie do większości ISA, RISC-V jest dostępny bez ograniczeń dla wszystkich użytkowników, pozwalając im na projektowanie, produkcję i sprzedaż układów oraz oprogramowania.

RV32IM RISC-V zastosowano w układach FPGA z rodziny IGLOO2, SmartFusion2 system-on-chip (SoC) i RTG4, wraz z zintegrowanym środowiskiem programistycznym SoftConsole. Środowisko to jest darmowe, oparte na platformie Eclipse i zawiera w pełni zintegrowany debugger, który umożliwia łatwy dostęp do zawartości pamięci, rejestrów oraz na wykonanie pojedynczej instrukcji. Całość umieszczona jest na Linuxie, a dzięki specjalnemu zestawowi narzędzi programistycznych Libero SoC Design Suite producent zapewnia pełne wspomaganie projektowe.