© 4designersart dreamstime.com

Komponenty |

Szybkie i energooszczędne pamięci magnetyczne od Toshiby

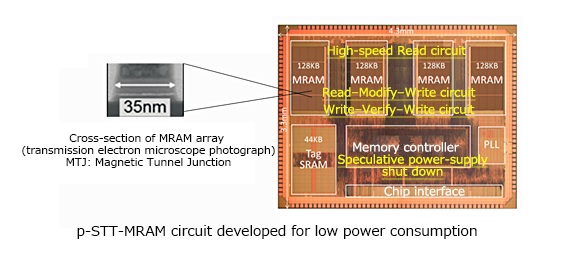

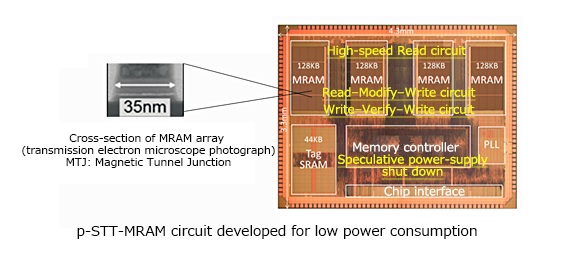

Toshiba opracowała nowe układy pamięci klasy 4-Mb wykorzystujące technologię STT-MRAM, nowy typ pamięci magnetycznej, zawierającej tranzystory krzemowe 65-nm, dedykowane wysokowydajnym procesorom oraz układom SoC (system-on-a-chip).

W ostatnich latach możemy obserwować rozrastanie się rynku układów scalonych wraz z powiększaniem się wachlarza ich zastosowań, do których możemy zaliczyć internet rzeczy, urządzenia noszone, smartfony, komputery stacjonarne , a także serwery w centrach danych. Jednocześnie wzrastają wymagania odnośnie jak najwyższej wydajności energetycznej oraz niskiego poboru mocy. W kontekście poboru mocy w wyżej wspomnianych układach półprzewodnikowych, redukcja mocy zużywanej przez bloki pamięci jest kluczowym kierunkiem ich rozwoju, szczególnie biorąc pod uwagę tendencję do umieszczania w tych układach pamięci SRAM (static random-access memory) o coraz większych rozmiarach. Szczególnie wysoka jest konsumpcja mocy zależna od prądów upływu wewnątrz pamięci, dlatego też eksperci Toshiby postanowili dalej rozwijać technologię pamięci nieulotnej Magnetic Tunneling Junction (MTJ), która oferuje dużą prędkość i niski pobór mocy. Eksperci oczekują, że uda się dokonać ewolucji od obecnie używanych pamięci ulotnych do pamięci nieulotnych.

Jednak ponieważ zużycie mocy zależne od zapisów pamięci i układów kontrolnych (układów peryferyjnych) jest wysokie, ogólna konsumpcja mocy nie jest wystarczająco niska, aby zastosować pamięć jako podręczną, nawet w przypadku matryc pamięci typu „normally-off”1 implementowanych z niższą konsumpcją mocy.

W celu rozwiązania problemów związanych ze stratami energii na skutek przepływu prądu, firma, we współpracy z grupą badawczą pod przewodnictwem profesora Hiroshi Nakamura z Wydziału Inżynierii Uniwersytetu w Tokio, opracowała układy zdolne do bardzo szybkiego włączania i wyłączania zasilania, z prędkościami umożliwiającymi wykonywanie tych czynności w zakresie 100-ns, aby umożliwić modułowi kontroli pamięci osiąganie pełnego stanu wyłączenia. Wykonano także odpowiednie ulepszenia, które pozwalają na odcięcie energii elektrycznej z dużą prędkością w układach nie potrzebujących zasilania, w zależności od stanu operacji wykonywanych w danej chwili na pamięci. Ponadto we współpracy z Uniwersytetem w Tokio, Toshiba opracowała algorytm monitorujący schematy dostępu do pamięci i przewidujący, jakie schematy dostępu będą prawdopodobnie realizowane jako następne. Algorytm jest implementowany w układzie kontroli pamięci. Dzięki zastosowaniu tej technologii, możliwe będzie zredukowanie konsumpcji mocy do mniej niż 1/10 zużywanej przez konwencjonalne, zintegrowane pamięci SRAM. Nowa pamięć charakteryzuje się także bardzo krótkim czasem odpowiedzi - 3.3 ns . Ta prędkość umożliwia zastosowanie jej jako pamięci podręcznej.

Technologia została szczegółowo przedstawiona na tegorocznej międzynarodowej konferencji IEEE - ISSCC( International Solid-State Circuits Conference), która odbyła się 2 lutego w Stanach Zjednoczonych, w San Francisco.

Wyżej opisane prace nad rozwojem pamięci magnetycznych są częścią projektu informatycznego „Normally-off”, prowadzonego przez organizację NEDO (New Energy and Industrial Technology Development Organization), we współpracy z zespołem pod kierownictwem profesora Hiroshi Nakamura z wydziału Inżynierii Uniwersytetu w Tokio. Toshiba będzie wprowadzać kolejne ulepszenia elementów pamięci magnetycznych, które zostały już przez nią opracowane oraz rozwijać nowe technologie pamięci, odpowiednie dla tranzystorów krzemowych o jeszcze mniejszych rozmiarach.

Foto: © Toshiba

1 - określenie odnoszące się do komputerów/pamięci aktywnie wyłączających podzespoły, których działanie nie jest konieczne w danej chwili do prawidłowego działania systemu, w celu zmniejszenia strat energetycznych.

Jednak ponieważ zużycie mocy zależne od zapisów pamięci i układów kontrolnych (układów peryferyjnych) jest wysokie, ogólna konsumpcja mocy nie jest wystarczająco niska, aby zastosować pamięć jako podręczną, nawet w przypadku matryc pamięci typu „normally-off”1 implementowanych z niższą konsumpcją mocy.

W celu rozwiązania problemów związanych ze stratami energii na skutek przepływu prądu, firma, we współpracy z grupą badawczą pod przewodnictwem profesora Hiroshi Nakamura z Wydziału Inżynierii Uniwersytetu w Tokio, opracowała układy zdolne do bardzo szybkiego włączania i wyłączania zasilania, z prędkościami umożliwiającymi wykonywanie tych czynności w zakresie 100-ns, aby umożliwić modułowi kontroli pamięci osiąganie pełnego stanu wyłączenia. Wykonano także odpowiednie ulepszenia, które pozwalają na odcięcie energii elektrycznej z dużą prędkością w układach nie potrzebujących zasilania, w zależności od stanu operacji wykonywanych w danej chwili na pamięci. Ponadto we współpracy z Uniwersytetem w Tokio, Toshiba opracowała algorytm monitorujący schematy dostępu do pamięci i przewidujący, jakie schematy dostępu będą prawdopodobnie realizowane jako następne. Algorytm jest implementowany w układzie kontroli pamięci. Dzięki zastosowaniu tej technologii, możliwe będzie zredukowanie konsumpcji mocy do mniej niż 1/10 zużywanej przez konwencjonalne, zintegrowane pamięci SRAM. Nowa pamięć charakteryzuje się także bardzo krótkim czasem odpowiedzi - 3.3 ns . Ta prędkość umożliwia zastosowanie jej jako pamięci podręcznej.

Technologia została szczegółowo przedstawiona na tegorocznej międzynarodowej konferencji IEEE - ISSCC( International Solid-State Circuits Conference), która odbyła się 2 lutego w Stanach Zjednoczonych, w San Francisco.

Wyżej opisane prace nad rozwojem pamięci magnetycznych są częścią projektu informatycznego „Normally-off”, prowadzonego przez organizację NEDO (New Energy and Industrial Technology Development Organization), we współpracy z zespołem pod kierownictwem profesora Hiroshi Nakamura z wydziału Inżynierii Uniwersytetu w Tokio. Toshiba będzie wprowadzać kolejne ulepszenia elementów pamięci magnetycznych, które zostały już przez nią opracowane oraz rozwijać nowe technologie pamięci, odpowiednie dla tranzystorów krzemowych o jeszcze mniejszych rozmiarach.

Foto: © Toshiba

1 - określenie odnoszące się do komputerów/pamięci aktywnie wyłączających podzespoły, których działanie nie jest konieczne w danej chwili do prawidłowego działania systemu, w celu zmniejszenia strat energetycznych.

Jednak ponieważ zużycie mocy zależne od zapisów pamięci i układów kontrolnych (układów peryferyjnych) jest wysokie, ogólna konsumpcja mocy nie jest wystarczająco niska, aby zastosować pamięć jako podręczną, nawet w przypadku matryc pamięci typu „normally-off”1 implementowanych z niższą konsumpcją mocy.

W celu rozwiązania problemów związanych ze stratami energii na skutek przepływu prądu, firma, we współpracy z grupą badawczą pod przewodnictwem profesora Hiroshi Nakamura z Wydziału Inżynierii Uniwersytetu w Tokio, opracowała układy zdolne do bardzo szybkiego włączania i wyłączania zasilania, z prędkościami umożliwiającymi wykonywanie tych czynności w zakresie 100-ns, aby umożliwić modułowi kontroli pamięci osiąganie pełnego stanu wyłączenia. Wykonano także odpowiednie ulepszenia, które pozwalają na odcięcie energii elektrycznej z dużą prędkością w układach nie potrzebujących zasilania, w zależności od stanu operacji wykonywanych w danej chwili na pamięci. Ponadto we współpracy z Uniwersytetem w Tokio, Toshiba opracowała algorytm monitorujący schematy dostępu do pamięci i przewidujący, jakie schematy dostępu będą prawdopodobnie realizowane jako następne. Algorytm jest implementowany w układzie kontroli pamięci. Dzięki zastosowaniu tej technologii, możliwe będzie zredukowanie konsumpcji mocy do mniej niż 1/10 zużywanej przez konwencjonalne, zintegrowane pamięci SRAM. Nowa pamięć charakteryzuje się także bardzo krótkim czasem odpowiedzi - 3.3 ns . Ta prędkość umożliwia zastosowanie jej jako pamięci podręcznej.

Technologia została szczegółowo przedstawiona na tegorocznej międzynarodowej konferencji IEEE - ISSCC( International Solid-State Circuits Conference), która odbyła się 2 lutego w Stanach Zjednoczonych, w San Francisco.

Wyżej opisane prace nad rozwojem pamięci magnetycznych są częścią projektu informatycznego „Normally-off”, prowadzonego przez organizację NEDO (New Energy and Industrial Technology Development Organization), we współpracy z zespołem pod kierownictwem profesora Hiroshi Nakamura z wydziału Inżynierii Uniwersytetu w Tokio. Toshiba będzie wprowadzać kolejne ulepszenia elementów pamięci magnetycznych, które zostały już przez nią opracowane oraz rozwijać nowe technologie pamięci, odpowiednie dla tranzystorów krzemowych o jeszcze mniejszych rozmiarach.

Foto: © Toshiba

1 - określenie odnoszące się do komputerów/pamięci aktywnie wyłączających podzespoły, których działanie nie jest konieczne w danej chwili do prawidłowego działania systemu, w celu zmniejszenia strat energetycznych.

Jednak ponieważ zużycie mocy zależne od zapisów pamięci i układów kontrolnych (układów peryferyjnych) jest wysokie, ogólna konsumpcja mocy nie jest wystarczająco niska, aby zastosować pamięć jako podręczną, nawet w przypadku matryc pamięci typu „normally-off”1 implementowanych z niższą konsumpcją mocy.

W celu rozwiązania problemów związanych ze stratami energii na skutek przepływu prądu, firma, we współpracy z grupą badawczą pod przewodnictwem profesora Hiroshi Nakamura z Wydziału Inżynierii Uniwersytetu w Tokio, opracowała układy zdolne do bardzo szybkiego włączania i wyłączania zasilania, z prędkościami umożliwiającymi wykonywanie tych czynności w zakresie 100-ns, aby umożliwić modułowi kontroli pamięci osiąganie pełnego stanu wyłączenia. Wykonano także odpowiednie ulepszenia, które pozwalają na odcięcie energii elektrycznej z dużą prędkością w układach nie potrzebujących zasilania, w zależności od stanu operacji wykonywanych w danej chwili na pamięci. Ponadto we współpracy z Uniwersytetem w Tokio, Toshiba opracowała algorytm monitorujący schematy dostępu do pamięci i przewidujący, jakie schematy dostępu będą prawdopodobnie realizowane jako następne. Algorytm jest implementowany w układzie kontroli pamięci. Dzięki zastosowaniu tej technologii, możliwe będzie zredukowanie konsumpcji mocy do mniej niż 1/10 zużywanej przez konwencjonalne, zintegrowane pamięci SRAM. Nowa pamięć charakteryzuje się także bardzo krótkim czasem odpowiedzi - 3.3 ns . Ta prędkość umożliwia zastosowanie jej jako pamięci podręcznej.

Technologia została szczegółowo przedstawiona na tegorocznej międzynarodowej konferencji IEEE - ISSCC( International Solid-State Circuits Conference), która odbyła się 2 lutego w Stanach Zjednoczonych, w San Francisco.

Wyżej opisane prace nad rozwojem pamięci magnetycznych są częścią projektu informatycznego „Normally-off”, prowadzonego przez organizację NEDO (New Energy and Industrial Technology Development Organization), we współpracy z zespołem pod kierownictwem profesora Hiroshi Nakamura z wydziału Inżynierii Uniwersytetu w Tokio. Toshiba będzie wprowadzać kolejne ulepszenia elementów pamięci magnetycznych, które zostały już przez nią opracowane oraz rozwijać nowe technologie pamięci, odpowiednie dla tranzystorów krzemowych o jeszcze mniejszych rozmiarach.

Foto: © Toshiba

1 - określenie odnoszące się do komputerów/pamięci aktywnie wyłączających podzespoły, których działanie nie jest konieczne w danej chwili do prawidłowego działania systemu, w celu zmniejszenia strat energetycznych.